Abstract

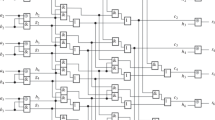

An (n, m) parallel counter is a circuit withn inputs that produces anm-bit binary count of the number of its inputs that are ONEs. This article reports on the design of large parallel counters with up to 1023 inputs. Design trade-offs are examined regarding the use of counter cells of size ranging from (3,2) to (31,5) as building blocks.

Similar content being viewed by others

References

L. Dadda, “Some Schemes for Parallel Multipliers,”Alta Frequenza, vol. 34, 1965, pp. 349–356.

L. Dadda, “On Parallel Digital Multipliers,”Alta Frequenza, vol. 45, 1976, pp. 574–580.

I.T. Ho and T.C. Chen, “Multiple Addition by Residue Threshold Functions and Their Representation by Array Logic,”IEEE Transactions on Computers, vol. C-22, 1973, pp. 762–767.

A. Svoboda, “Adder with Distributed Control,”IEEE Transactions on Computers, vol. C19, 1970, pp. 749–751.

E.E. Swartzlander, Jr. and R.F. Jones, Jr., “Digital Neural Network Implementation,”Proceedings of the 11th Annual International Phoenix Conference on Computers and Communications, 1992, pp. 722–728.

E.E. Swartzlander, Jr., “Parallel Counters,”IEEE Transactions on Computers, vol. C-22, 1973, pp. 1021–1024.

D. Zhang, G.A. Jullien, W.C. Miller, and Earl Swartzlander, Jr., “Arithmetic for Digital Neural Networks,”Proceedings of the 10th Symposium on Computer Arithmetic, 1991, pp. 58–63.

E.E. Swartzlander, Jr., “The Quasi-Serial Multiplier,”IEEE Transactions on Computers, vol. C-22, 1973, pp. 317–321.

R.F. Jones, Jr. and Earl E. Swartzlander, Jr., “Parallel Counter Implementation,”Proceedings of the 26th Asilomar Conference on Signals, Systems & Computers, 1992, pp. 381–385.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Jones, R.F., Swartzlander, E.E. Parallel counter implementation. Journal of VLSI Signal Processing 7, 223–232 (1994). https://doi.org/10.1007/BF02409399

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/BF02409399