Abstract

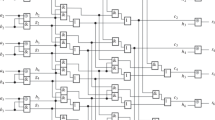

The “Wallace Tree/Dadda Fast Multiplier” consists of the following three steps: 1) form a bit-product matrix; 2) reduce the bit-product matrix to two rows; and 3) sum the two rows. This article describes a novel approach to implementing the second step. The new second step is accomplished with sorting and parity generation logic. This is very different from the Wallace/Dadda method, which uses full and half adders to reduce the bit-product matrix.

This approach yields a multiplier that is faster than a Wallace/Dadda multiplier when multiplying small numbers. However, this method also requires more gates to implement.

Similar content being viewed by others

References

C.S. Wallace, “A Suggestion for a Fast Multiplier,”IEEE Transactions on Electronic Computers, vol. EC-13, 1964, pp. 14–17, (reprinted in [4]).

L. Dadda, “Some Schemes for Parallel Multipliers,”Alta Frequenza, vol. 34, 1965, pp. 349–356, (reprinted in [4]).

A. Svoboda, “Adder with Distributed Control,”IEEE Transactions on Computers, vol. C-19, 1970, pp. 749–751, (reprinted in [4]).

E.E. Swartzlander, Jr.,Computer Arithmetic, Los Alamitos CA: IEEE Computer Society Press, 1990.

B.C. Drerup and Earl E. Swartzlander, Jr., “Fast Multiplier Bit-Product Matrix Reduction Using Bit-Ordering and Parity Generation,”Proceedings of the 26th Asilomar Conference on Signals, Systems & Computers, 1992, pp. 356–360.

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Drerup, B.C., Swartzlander, E.E. Fast multiplier bit-product matrix reduction using bit-ordering and parity generation. Journal of VLSI Signal Processing 7, 249–257 (1994). https://doi.org/10.1007/BF02409401

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/BF02409401