Abstract

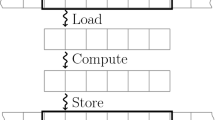

The study of Regular Iterative Algorithms (RIAs) was introduced in a seminal paper by Karp, Miller, and Winograd in 1967. In more recent years, the study of systolic architectures has led to a renewed interest in this class of algorithms, and the class of algorithms implementable on systolic arrays (as commonly understood) has been identified as a precise subclass of RIAs. In this paper, we shall study the dependence structure of RIAs that are not systolic; examples of such RIAs include matrix pivoting algorithms and certain forms of numerically stable two-dimensional filtering algorithms. It has been shown that the so-called hyperplanar scheduling for systolic algorithms can no longer be used to schedule and implement non-systolic RIAs. Based on the analysis of a so-called computability tree we generalize the concept of hyperplanar scheduling and determine linear subspaces in the index space of a given RIA such that all variables lying on the same subspace can be scheduled at the same time. This subspace scheduling technique is shown to be asymptotically optimal, and formal procedures are developed for designing processor arrays that will be compatible with our scheduling schemes. Explicit formulas for the schedule of a given variable are determined whenever possible; subspace scheduling is also applied to obtain lower dimensional processor arrays for systolic algorithms.

Similar content being viewed by others

References

R.M. Karp, R.E. Miller, and S. Winograd. The organization of computations for uniform recurrence equations.JACM 14:563–590, 1967.

H.V. Jagadish, S.K. Rao, and T. Kailath. Multi-processor architectures for iterative algorithms.Proceedings of the IEEE, 75, No. 9:1304–1321, Sept. 1987.

S.K. Rao,Regular Iterative Algorithms and their Implementation on Processor Arrays. PhD thesis, Stanford University, Stanford, Calafornia, 1985.

S.K. Rao and T. Kailath. Regular iterative algorithms and their implementations on processor arrays.Proc. IEEE, 76, No. 2:259–282, March 1988.

S.Y. Kung.VLSI Array Processors. Prentice Hall Series, 1987.

S.K. Rao.Systolic Arrays and their Extensions. Prentice Hall Series, to appear, 1988.

V .P. Roychowdhury, S. K. Rao, L. Thiele, and T. Kailath. On the localization of algorithms for VLSI processor arrays.1988 Workshop On VLSI Signal Processing, pages 459–470, Nov. 1988.

V.P. Roychowdhury, L. Thiele, S.K. Rao, and T. Kailath. On the localization of algorithms for VLSI processor arrays. Submitted toIEEE Trans. Computers, October, 1988.

H.T. Kung. Let’s design algorithms for VLSI systems. InProc. Caltech Conf on VLSI, pages 65–90, Jan. 1979.

H.T. Kung. Why systolic architectures?IEEE Computer Magazine, 25:37–46, Jan. 1980.

H.T. Kung and C,E, Leiserson, Systolic arrays for VLSI. InSparse Matrix Proceedings, pages 245–282. Philadelphia Society of Industrial and Applied Mathematicians, 1978.

D.I. Moldovan. On the analysis and synthesis of VLSI algorithms.IEEE Trans. Computers, C-31:1121–1126, Nov. 1982.

D.I. Moldovan. On the design of algorithms for VLSI systolic arrays.Proc. IEEE, pages 113–120, Jan. 1983.

J.A.B. Fortes.Algorithm transformations for parallel processing and VLSI architectures. PhD thesis, University of Southern California, Los Angeles, Dec. 1983.

P. Quinton. The systematic design of systolic arrays. Technical report, INRIA Report, Paris, 1983.

P.R. Capello and K. Steiglitz, Unifying VLSI array design with linear transformations of space-time.Advances in Computing Research, 2:23–65, 1984.

V.P. Roychowdhury and T. Kailath. Study of parallelism in regular iterative algorithms. Submitted to SIAM Journal of Computing, Dec. 1988.

Vwani P. Roychowdhury.Derivation, Extensions and Parallel Implementation of Regular Iterative Algorithms. PhD thesis, Department of Electrical Engineering, Stanford University, Stanford, California, December 1988.

W.M. Waite. Path detection in niulti-dimensional iterative arrays.JACM, 14, 1967.

C.H. Papadimitriou and K. Steiglitz.Combinatorial Optimization: Algorithms and Complexity. Prentice Hall. 1982.

M. Behzad, G. Chartrand, and L. Lesniak-Foster.Graphs and Digraphs. Prindle, Weber and Schmidt International Series, 1979.

V.P. Roychowdhury and T. Kailath. Regular processor arrays for matrix algorithms with pivoting. Submitted toCACM, Feb. 1988.

V.P. Roychowdhury and T. Kailath. Regular processor arrays for matrix algorithms with pivoting,Int. Conference on Systolic Arrays, pages 237–246, May 1988.

D.I. Moldovan and J.A.B. Fortes. Partitioning and mapping of algorithms into fixed size systolic arrays.IEEE Trans. Computers, No. 1:1–12, January 1986.

Author information

Authors and Affiliations

Additional information

This work was supported in part by the SDIO/IST, managed by the Army Research Office under Contract DAAL03-87-K-0033 and by the Department of the Navy, Office of Naval Research under Contract N00014-86-K-0726.

Rights and permissions

About this article

Cite this article

Roychowdhury, V.P., Kailath, T. Subspace scheduling and parallel implementation of non-systolic regular iterative algorithms. J VLSI Sign Process Syst Sign Image Video Technol 1, 127–142 (1989). https://doi.org/10.1007/BF02477178

Received:

Published:

Issue Date:

DOI: https://doi.org/10.1007/BF02477178