Abstract

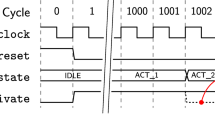

The functional-level test has been proposed as an alternative to reduce the complexity of test when VLSI gets larger and more complicated. It has been successful for circuits such as memories, PLAs and microprocessors. However, the functional-level test for general functional models has seldom been studied. This paper presents an object-oriented VLSI model and a functional-level fault simulation methodology for general functional model. Based on the proposed VLSI model, FFS (functional-level Fault Simulator) with friendly visual interface has been implemented on Microsoft Windows platform by use of C++. It is an integral part of FMVS (Functional test Modeling and Verification System)—an extended subsystem of TeDS (Test Development System). The goal of FFS is to determine the fault coverage, generate fault dictionary and compact original test set at the function-level. In order to be efficient, FFS uses the concurrent and parallel mechanisms by taking advantage of the object-oriented VLSI model. The object-oriented VLSI model based fault simulation has been validated in the functional-level test by simulation results and the satisfying performance of FFS.

Similar content being viewed by others

Explore related subjects

Discover the latest articles, news and stories from top researchers in related subjects.References

Hong S J. Fault simulation strategy for combinational logic networks. InProc. 8th FTCS, 1978, pp. 96–99.

Antreich K J, Schulz M H. Accelerated fault simulation and fault grading in combinational circuits.IEEE-Trans. on CAD, 1987, 6: 704–712.

Harel D, Sheng R, Udell J. Eefficient single fault propagation in combinational circuits. InProc. ICCAD, Nov., 1987, pp. 2–5.

Maamari F, Rajski J. A method of fault simulation based on stem regions.IEEE Trans. on CAD, 1990, 9: 212–220.

Maamari F, Rajski J. The dynamic reduction of fault simulation. InProc. Int’l Test Conf., Sept., 1990, pp. 801–808.

Xing Y, van Brakel G, Kerkhoff H G. Accelerated fault simulation utilizing multiple-fault propagation. InFirst Asian Test Symposium, Nov., 1992, pp. 34–39.

Wang Peijie, Zhang Yingzhong, Zhou Jingang The Object-oriented Programming Techniques for WINDOWS. Dalian Institute of Technology Press, 1994.

Wang Chengwei, Zheng Xiaojun, Peng Muchang. The Object-oriented Analysis, Design and Application. The National Defense Industry Press, 1994.

Mark C Hansen, John P Hayes. High-level test generation using symbolic scheduling. InProc. Int’l Test Conf., 1995, pp.586–595.

Texas Instruments Inc., TAAC Gate Arrays, 1988.

Bechir Ayari, Bozena Kaminska. Cyclogen: Automatic, functional-level test generator. InFirst Asian Test Symposium, Nov., 1992, pp. 124–129.

Chang Jau-Shien, Lin Chen-Shang. Test set compaction for combinational circuits. InFirst Asian Test Symposium, Nov., 1992, pp.20–25.

Yang Qiaolin. Test development system: An introduction to TeDS. Theses, Reports and Documents of Test Development System, Institute of Computing Technology, Chinese Academy of Sciences, 1995.

Liu Qin, Wei Daozheng. The research and implementation of parallel fault simulation for digital circuits.Journal of Computer-Aided Design & Computer Graphics, 1992, 4(2): 8–13.

Shi Yuan, Yang Qiaolin. The research of functional test modeling and verification. Collected Papers of the 4th Computer Science and Technology Seminar of Graduate Students, Academia Sinica, 1996.

Author information

Authors and Affiliations

Additional information

Li Wei received his M.S. degree in computer science from Harbin Institute of Technology in 1989. He is currently a Ph.D. candidate in computer science at Institute of Computing Technology, Chinese Academy of Sciences. His main research interests include VLSI test software, object-oriented and visualization technology.

Yang Qiaolin was born in 1940. He received his B.S. degree from Peking University in 1963. He is a Professor at the Institute of Computing Technology, Chinese Academy of Sciences. His research interests include software engineering, computer-aided design and test and distributed object computing.

Rights and permissions

About this article

Cite this article

Li, W., Yang, Q. Functional-level Fault Simulation with concurrent and parallel mechanisms using object-oriented VLSI model. J. of Comput. Sci. & Technol. 13, 147–160 (1998). https://doi.org/10.1007/BF02946603

Received:

Revised:

Issue Date:

DOI: https://doi.org/10.1007/BF02946603