Abstract

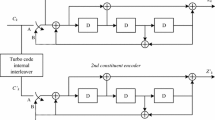

This paper presents a block turbo decoding algorithm, from its theory to its implementation in a programmable circuit. In this study, we discuss the two prototypes realized. It will be possible to compare the complexity of the core of the process, which is the elementary decoder, thanks to the choice of essential parameters. One prototype is more dedicated to high data rates, the other one being implemented on only one FPGA which means a gain in terms of area.

First, we briefly focus on the description of the siso (Soft-In Soft-out) algorithm used to implement the turbo decoder. Then, we explain the essential choices in order to adapt the algorithm for an ASIC implementation, which leads to a compromise between area and binary error rate. Finally, we present the two prototypes implemented and their experimental results.

Résumé

L’objectif de cet article est de présenter le turbodecodage de codes produits depuis la théorie jusqu’à la réalisation sur circuit programmable. Deux prototypes ont été réalisés, Us serviront de support à cette étude. Il sera en effet possible de comparer la complexité du décodeur élémentaire en fonction d’un certain nombre de paramètres, de mettre face à face une structure dédiée aux débits élevés et une structure optimisée en surface.

Dans une première partie, on trouvera une brève description de l’algorithme srso (Soft-In Soft-Out) permettant de réaliser le turbo décodage. Vient ensuite la description de l’adaptation de cet algorithme à l’implantation sur silicium. Cette phase nécessite des choix entre complexité en terme de circuit et performance en terme de taux d’erreurs binaires. La dernière partie présente les choix d’architectures et les résultats expérimentaux des 2 prototypes.

Similar content being viewed by others

References

Berrou (C), Glavieux (A.), Thttimajshima (P.), “Near Shannon limit error-correcting coding and decoding: Turbo-codes”,Ieee Int. Conf. on Com. ICC’ 93, May 1993,2/3, pp. 1064–1071.

Pyndiah (R.), Glavieux (A.), A.Picart (A.), Jacq (S.), “Near optimum decoding of product codes”, in proc. ofieee globecom ‘94Conference, Nov-Dec. 1994, San Francisco,1/3, pp. 339- 343.

Pyndiah (R.), “Near optimum decoding of product codes: Block Turbo Codes”,ieee Trans. on Comm., Aug. 1998,46, no 8, pp. 1003–1010.

Pyndiah (R.), “Iterative decoding of product codes: block turbo code”,Int. Symposium on turbo codes and related topics, Brest, Sept. 1997, pp. 71–79.

Chase (D.), “A class of algorithms for decoding block codes with channel measurement information”,ieee Trans. Inform. Theory, Jan. 1972,IT-18, pp. 170–182.

Kaneko (T), Nishijima (T), Inazumi (H.), Hirasawa (S.), “An efficient maximum-likelihood-decoding algorithm for linear block codes with algebraic decoder”,ieee Trans. Inform. Theory, Mar. 1994,40, pp. 320–3327.

Dave (S.), Kim (J.), Kwatra (S.C.), “An efficient decoding algorithm for Bloc Turbo Codes”,ieee Trans. On Communications, Jan. 2001,49, no l, pp 41–46.

Adde (P.), Pyndiah (R.), Raoul (O.), Inisan (J.R.), “Block turbo decoder design”, Int. Symposium on turbo codes and related topics, Brest, Sept. 1997, pp. 166–169.

Adde (P.), Pyndiah (R.), Raoul (O.), “Performance and complexity of block turbo decoder circuits”,Third International Conference on Electronics, Circuits and System icecs’96, 13–16 Oct. 1996 - Rodos, Greece, pp. 172–175.

Kerouédan (S.), Adde (P.), Ferry (P.), “Comparaison performances/ complexité de décodeurs de codes bch utilises en turbo- décodage”.Gretsi’99, 13/17 Sept.1999.

Adde (P.), Pyndiah (R.), Buda (F.), “Design and performance of a product code turbo encoding-decoding prototype”,Annals of telecommunications,54, no 3–4, pp. 214–219.

Raoul (O.), Adde (P.), Pyndiah (R.), “Architecture et conception d’un circuit turbo-décodeur de codes produits,”GRETSI’95, Juan-Les-Pins, Sept. 1995, pp. 981–984.

Adde (P.), Pyndiah (R.), Inisan (J.R.), Sichez (Y.), “Conception d’un turbo décodeur de code produit”,gretsi’97, Sept. 1997, Grenoble, pp. 1169–1172.

Kerouédan (S.), Adde (P.), “Implementation of a block turbo decoder in a single chip”, 2nd International Symposium on Turbo Codes and Related Topics, 3/7 Sept.2000, Brest.

Adde (P.), Pyndiah (R.), “Recent simplification and improvement of block turbo code”, 2nd International Symposium on Turbo Codes and Related Topics,3/7 Sept.2000, Brest.

Goalic (A.), Pyndiah (R.), “Real time turbo decoding of product codes on a digital signal processor”, Int. Symposium on turbo codes and related topics, Brest, Sept. 1997.

Robert (S.), “Les turbo codes en blocs”, séminaire UBS, Lorient, Feb. 2001.

Author information

Authors and Affiliations

Corresponding authors

Rights and permissions

About this article

Cite this article

Kerouédan, S., Adde, P. & Pyndiah, R. How we implemented block turbo codes?. Ann. Télécommun. 56, 447–454 (2001). https://doi.org/10.1007/BF02995455

Received:

Accepted:

Issue Date:

DOI: https://doi.org/10.1007/BF02995455