Abstract

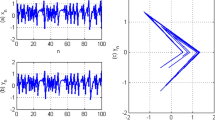

This paper presents the latest results on a block turbo decoder design. We propose a block turbo decoder circuit for the error protection of small data blocks such asAtm cells on anAwgn (additive white Gaussian noise) channel with a code rate close to 0.5. A prototype was developed atEnst Bretagne. It allowsBer (bit error rate) measurements down to 10−9 and uses programmable gate arrays (Fpga Xilinx circuits). The elementary extendedBch code and the data block size can be modified to fit specifications of different applications.

Résumé

Cet article présente les derniers résultats concernant un turbo décodeur de code en blocs. Un circuit turbo décodeur permet la correction d’erreurs dans de petits blocs de données tels que ceux utilisés pour les cellulesAtm avec un rendement proche de 0,5. Une maquette a été développée à l’Enst Bretagne simulant un canal gaussien. Elle permet de mesurer de faibles taux d’erreurs binaires (jusqu’à 10−9) et utilise des circuits intégrés programmables (circuits Xilinx). Le codeBch étendu utilisé comme code élémentaire pour le turbo code et la taille du bloc de données peuvent être modifiés afin de les adapter à différentes applications.

Similar content being viewed by others

References

Berrou (C.), Glavieux (A.), Thitimajshima (P.). Near Shannon limit error-correcting coding and decoding: Turbo codes (1),IEEE Int. Conf. on Comm.ICC’93,2/3, pp. 1064–1071, (May 1993).

Pyndiah (R.).Glavieux (A.), Picart (A.),Jacq (S.). Near optimum decoding of product codes, in proc. ofIEEE GLOBECOM ’94Conference,1/3, San Francisco, pp. 339–343, (Nov.-Dec. 1994).

Pyndiah (R.). Near optimum decoding of product codes: Block Turbo Codes,IEEE Trans, on Comm.,46, no 8, pp. 1003–1010, (Aug. 1998).

Bahl (L. R.), Cocke (J.), Jelinek (F.), Raviv (J.). Optimal decoding of linear codes for minimizing symbol error rate,IEEE Trans. IT, pp. 284–287, (March 1974).

Elias (P.). Error-free coding,IRE Trans, on Inf. Theory.4, pp. 29–37, (Sept. 1954).

Pyndiah (R.). Iterative decoding of product codes: block turbo code,Int. Symposium on turbo codes and related topics, Brest, pp. 71–79, (Sept. 1997).

Adde (P.), Pyndiah (R.), Raoul (O.). Performance and complexity of block turbo decoder circuits.Third International Conference on Electronics, Circuits and System ICECS’96, pp 172–175, Rodos, Greece, (13–16, Oct. 1996).

Goalic (A.), Pyndiah (R.). Real time turbo decoding of product codes on a digital signal processor.Int. Symposium on turbo codes and related topics, Brest, (Sept. 1997).

Chase (D.). A class of algorithms for decoding block codes with channel measurement information,IEEE Trans. IT. 18, pp. 170–182, (Jan. 1972).

Adde (P.), Pyndiah (R.). Raoul (O.), Inisan (J. R.). Block turbo decoder design,Int. Symposium on turbo codes and related topics, Brest, pp. 166–169. (Sept. 1997).

Adde (P.), Pyndiah (R.), Inisan (J. R.), Sichez (Y.). «Conception d’un turbo décodeur de code produit»,GRETSI’97, Grenoble, pp. 1169–1172, (Sept. 1997).

Jezequel (M.), Berrou (C.), Inisan (J. R.), Sichez (Y.). Test of a turbo-encoder/decoder,Turbo Coding Seminar, Lund, Sweden, pp. 35–41,(28–29, Aug. 1996).

Author information

Authors and Affiliations

Rights and permissions

About this article

Cite this article

Adde, P., Pyndiah, R. & Buda, F. Design and performance of a product code turbo encoding-decoding prototype. Ann. Télécommun. 54, 214–219 (1999). https://doi.org/10.1007/BF02998582

Received:

Issue Date:

DOI: https://doi.org/10.1007/BF02998582