Abstract

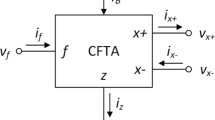

In this paper, a method for reducing the parasitic impedance effects of the current feedback operational amplifiers (CFOAs) in an inductor simulator at low frequencies is proposed. Also, two novel grounded inductors employing a current follower (CF) and a second generation current conveyor (CCII) are given to illustrate the parasitic reduction technique clearly. The low frequency restrictions of the proposed inductors due to terminal parasitic resistances can be improved by using the presented parasitic impedance reduction technique. SPICE simulations show that the presented inductor employing CFOAs in a voltage-mode (VM) band-pass and high-pass filter application has lower parasitic effects at low frequencies. In addition to simulation results, experimental test results are given to verify the theory.

Similar content being viewed by others

References

S.A. Al-Walaie, M.A. Alturaigi, Current mode simulation of lossless floating inductance. Int. J. Electron. 83(6), 825–829 (1997)

O. Cicekoglu, New current conveyor based active-gyrator implementation. Microelectron. J. 29(8), 525–528 (1998)

O. Cicekoglu, A. Toker, H. Kuntman, Universal immittance function simulators using current conveyors. Comput. Electr. Eng. 27, 227–238 (2001)

A. Fabre, Gyrator implementation from commercially available transimpedance operational amplifiers. Electron. Lett. 28(3), 263–264 (1992)

A. Fabre, H. Barthelemy, Composite second-generation current conveyor with reduced parasitic resistance. Electron. Lett. 30(5), 377–378 (1994)

A. Fabre, O. Saaid, F. Wiest, C. Boucheron, High frequency applications based on a new current controlled conveyor. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 43, 82–91 (1996)

G. Ferri, N. Guerrini, High-valued passive element simulation using low-voltage low-power current conveyors for fully integrated applications. IEEE Trans. Circuits Syst. II Analog Digit. Signal Process. 48(4), 405–409 (2001)

G. Ferri, N.C. Guerrini, Low-Voltage Low-Power CMOS Current Conveyors (Kluwer Academic, Dordrecht, 2003)

G. Ferri, N.C. Guerrini, M. Diqual, CCII-based floating inductance simulator with compensated series resistance. Electron. Lett. 39, 1560–1562 (2003)

C. Giannì, S. Pennisi, G. Scotti, A. Trifiletti, The universal circuit simulator: a mixed signal approach to n-port network and impedance synthesis. IEEE Trans. Circuits Syst. I 54(10), 2178–2183 (2007)

M. Gulsoy, O. Cicekoglu, Lossless and lossy synthetic inductors employing single current differencing buffered amplifier. IEICE Trans. Commun. E88B(5), 2152–2155 (2005)

M. Higashimura, Y. Fukui, Novel method for realizing lossless floating admittance using current conveyors. Electron. Lett. 23(10), 498–499 (1987)

W. Kiranon, P. Pawarangkoon, Floating inductance simulation based on current conveyors. Electron. Lett. 33, 1748–1749 (1997)

M.C. Layos, I. Haritantis, On the derivation of current-mode floating inductors. Int. J. Circuit Theory Appl. 25(1), 29–36 (1997)

S. Minaei, E. Yuce, O. Cicekoglu, A versatile active circuit for realising floating inductance, capacitance, FDNR and admittance converter. Analog Integr. Circuits Signal Process. 47(2), 199–202 (2006)

G. Palumbo, S. Pennisi, A technique for the reduction of the input resistance of current-mode circuits electronics, in IEEE International Conference, ICECS, vol. 2 (1998), pp. 279–282

O. Saaid, A. Fabre, Class AB current controlled resistance for high performance current mode applications. Electron. Lett. 32, 4–5 (1996)

A.S. Sedra, K.C. Smith, A second-generation current conveyor and its applications. IEEE Trans. Circuit Theory 17(1), 132–134 (1970)

A.S. Sedra, K.C. Smith, Microelectronic Circuits, 4th edn. (Oxford University Press, London, 1998), p. 4

F. Seguin, A. Fabre, New second generation current conveyor with reduced parasitic resistance and bandpass filter application. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 48, 781–785 (2001)

R. Senani, On the realization of floating active elements. IEEE Trans. Circuits Syst. CAS-33(3), 323–324 (1986)

L. Serrano, A. Carlosena, GB-R impedances: new approach to impedance simulation. Electron. Lett. 31(9), 689–690 (1995)

V. Singh, On floating impedance simulation. IEEE Trans. Circuits Syst. 36(1), 161–162 (1989)

A.M. Soliman, New active-gyrator circuit using a single current conveyor. Proc. IEEE 66, 1580–1581 (1978)

W. Surakampontorn, Accurate CMOS-based current conveyors. IEEE Trans. Instrum. Meas. 40, 699–702 (1991)

A. Toker, O. Cicekoglu, H. Kuntman, New active gyrator circuit suitable for frequency-dependent negative resistor implementation. Microelectron. J. 30, 59–62 (1999)

P.M. Trabulo, D.A. Duraes, P.M. Mendes, P.J. Garrido, J.H. Correia, Spiral inductors on silicon for wireless communications. Mat. Sci. Forum 455–456, 116–119 (2004)

Z. Wang, Novel voltage-controlled grounded resistor. Electron. Lett. 26, 1711–1712 (1990)

E. Yuce, Inductor implementation using a canonical number of active and passive elements. Int. J. Electron. 94(4), 317–326 (2007)

E. Yuce, Negative impedance converter with reduced non-ideal gain and parasitic impedance effects. IEEE Trans. Circuits Syst. I Regul. Pap. 55(1), 264–271 (2008)

E. Yuce, Grounded inductor simulators with improved low frequency performances. IEEE Trans. Instrum. Meas. 57(5), 1079–1084 (2008)

E. Yuce, O. Cicekoglu, The effects of non-idealities and current limitations on the simulated inductances employing current conveyors. Analog Integr. Circuits Signal Process. 46(2), 103–110 (2006)

E. Yuce, S. Minaei, A modified CFOA and its applications to simulated inductors, capacitance multipliers, and analog filters. IEEE Trans. Circuits Syst. I Regul. Pap. 55(1), 254–263 (2008)

E. Yuce, S. Minaei, Universal current-mode filters and parasitic impedance effects on the filter performances. Int. J. Circuit Theory Appl. 36, 161–171 (2008)

E. Yuce, S. Minaei, O. Cicekoglu, A novel grounded inductor realization using a minimum number of active and passive components. ETRI J. 27(4), 427–432 (2005)

E. Yuce, S. Minaei, O. Cicekoglu, Limitations of the simulated inductors based on a single current conveyor. IEEE Trans. Circuits Syst. I Regul. Pap. 53(12), 2860–2867 (2006)

E. Yuce, S. Minaei, O. Cicekoglu, Full-wave rectifier realization using only two CCII+s and NMOS transistors. Int. J. Electron. 93(8), 533–541 (2006)

Author information

Authors and Affiliations

Corresponding author

About this article

Cite this article

Yuce, E., Minaei, S. On the Realization of Simulated Inductors with Reduced Parasitic Impedance Effects. Circuits Syst Signal Process 28, 451–465 (2009). https://doi.org/10.1007/s00034-008-9093-0

Received:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-008-9093-0