Abstract

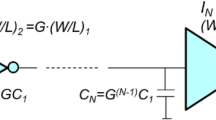

Signal propagation delay on a multi-source multi-sink bidirectional bus has a dominant effect on high-performance chips. This work presents a novel greedy algorithm that minimizes the critical propagation delay of an RLC-based bus. Based on the topology of a multi-source multi-sink bus and the RLC delay model, the proposed algorithm inserts signal repeaters into the critical path of the RLC-based bus and adjusts their sizes to minimize the maximal propagation delay. This procedure is repeated until no additional improvement is needed. Several buses with various topologies are tested using the proposed algorithm in deep submicron technologies. Experimentally, the critical delay in an RLC-based bus can be reduced dramatically by up to 62.4% with inserted repeater sizes of 24 and execution time of 1.65 s on average. Moreover, average delay reduction, repeater sizes, and running time for 0.18 μm technology are 5.8%, 6.4%, and 26.2%, respectively, better than those of 0.35 μm. Additionally, the topologies of all of the RLC-based buses with inserted repeaters in deep submicron technologies are simulated using HSPICE. The error ratio in the critical delay of a bus with inserted repeaters determined by comparison with HSPICE is 2.7% on average. The proposed algorithm is simple and extremely practical.

Similar content being viewed by others

References

0.35UM Logic Silicide (SPQM, 3.3V) Spice Models, TSMC (1996)

T.-C. Chen, S.-R. Pan, Y.-W. Chang, Performance optimization by wire and sizing under the transmission line model, in Proc. of International Conference on Computer Design (September 2001), pp. 23–26

T.-C. Chen, S.-R. Pan, Y.-W. Chang, Timing modeling and optimization under the transmission line model. IEEE Trans. VLSI Syst. 12(1) (2004)

J. Cong, D.Z. Pan, Interconnect delay estimation models for synthesis and design planning, in Proc. ASP-DAC (1999), pp. 97–100

W.C. Elmore, The transient response of damped linear networks. J. Appl. Phys. 19, 55–63 (1948)

M. Ghoneima, Y. Ismail, Optimum positioning of interleaved repeaters in bidirectional buses. IEEE Trans. CAD Integr. Circuits Syst. 24(3), 461–669 (2005)

Y.I. Ismail, E.G. Friedman, Optimum repeater insertion based on a COMS delay model for on-chip RLC interconnect, in Proc. 11th IEEE International Conference on ASIC (1998), pp. 369–373

Y.I. Ismail, E.G. Friedman, Effects of inductance on the propagation delay and repeater insertion in VLSI circuits. IEEE Trans. Very Large Scale Integr. Syst. 8(2), 195–206 (2000)

Y.I. Ismail, E.G. Friedman, J.L. Neves, Equivalent Elmore delay for RLC trees. IEEE Trans. CAD Integr. Circuits Syst., 83–97 (2000)

Y.I. Ismail, E.G. Friedman, J.L. Neves, Repeater insertion in tree structured inductive interconnect. IEEE Trans. Circuits Syst. II: Analog Digit. Signal Process. 48(5), 471–481 (2001)

D.-Y. Kao, C.-C. Tsai, C.-K. Cheng, T.-T. Lin, New design and implementation for signal repeaters, in The Sixth VLSI Design/CAD Workshop (August 1995), pp. 173–176

D. Lehther, S.S. Sachin, Sapatnekar, Moment-based techniques for RLC clock tree construction. IEEE Trans. Circuits Syst. II: Analog Digit. Signal Process. 45(1) (1998)

J. Lillis, C.-K. Cheng, T.-T.Y. Lin, Simultaneous routing and buffer insertion for high performance interconnect, in Proc. Sixth Great Lakes Symposium on VLSI (1996), pp. 148–153

C.-A. Lin, C.-H. Wu, Second-order approximations for RLC trees. IEEE Trans. CAD Integr. Circuits Syst. 23(7), 1124–1128 (2004)

P. Sarkar, C.K. Koh, Routability-driven repeater block planning for interconnect-centric floorplanning. IEEE Trans. CAD Integr. Circuits Syst. 660–671 (2001)

C.-C. Tsai, Timing driven based on signal repeater insertion. J. Natl. Taipei Univ. Technol. 31(2), 111–133 (1998)

C.-C. Tsai, D.-Y. Kao, C.-K. Cheng, Performance driven bus buffer insertion. IEEE Trans. CAD Integr. Circuits Syst., 429–437 (1996)

R. Venkatesan, J.A. Davis, J.D. Meindl, Compact distributed RLC interconnect models—part IV: unified models for time delay, crosstalk, and repeater insertion. IEEE Trans. Electron Dev. 50(4), 1094–1102 (2003)

S.-L. Wang, Y.-W. Chang, Accurate delay formulae for buffer RLC trees, in The 14th VLSI Design/CAD Symposium, paper A2-2 (August 2003)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Tsai, CC., Wu, JO. & Lee, TY. Maximal Delay Reduction for RLC-Based Multi-Source Multi-Sink Bus with Repeater Insertion. Circuits Syst Signal Process 28, 805–817 (2009). https://doi.org/10.1007/s00034-009-9132-5

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-009-9132-5