Abstract

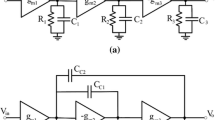

In this paper, we present an AC-boosting compensation topology with double pole-zero cancellation (ACBC-DPZ) for a multistage amplifier driving a very large capacitive load. The proposed technique modifies the original AC-boosting compensation (ACBC) topology to increase the power-bandwidth efficiency and reduce the size for the output power transistor and compensation capacitor. Simulation results show that the ACBC-DPZ amplifier using a CSM 0.18 μm CMOS process can achieve a unity gain bandwidth of 14 MHz and an average slew rate of 3.88 V/μs at 1500 pF load. The amplifier dissipates 2.55 mW at a 1.8 V supply.

Similar content being viewed by others

References

R.J. Apfel, P.R. Gray, A fast-settling monolithic operational amplifier using doublet compression techniques. IEEE J. Solid-State Circuits 9, 332–340 (1974)

P.K. Chan, Y.C. Chen, Gain-enhanced feedforward path compensation technique for pole zero cancellation at heavy capacitive loads. IEEE Trans. Circuits Syst. II 50, 933–941 (2003)

R.G.H. Eschauzier, L.P.T. Kerklaan, J.H. Huijsing, A 100-MHz 100-dB operational amplifier with multipath nested Miller compensation structure. IEEE J. Solid-State Circuits 27, 1709–1717 (1992)

X.H. Fan, C. Mishra, E. Sanchez-Sinencio, Single Miller capacitor frequency compensation technique for low-power multistage amplifiers. IEEE J. Solid-State Circuits 40, 584–592 (2005)

H.C. Foong, M.T. Tan, An analysis of THD in class D amplifiers, in Proc. IEEE Asia Pacific Conf. Circuits and Systems, Singapore, December 2006, pp. 724–727

J.H. Huijsing, Multistage amplifier with capacitive nesting for frequency compensation. U.S. Patent 602 234, April 1984

H. Lee, K.N. Leung, P.K.T. Mok, A dual-path bandwidth extension amplifier topology with dual-loop parallel compensation. IEEE J. Solid-State Circuits 38, 1739–1744 (2003)

H. Lee, P.K.T. Mok, Active-feedback frequency-compensation technique for low-power multistage amplifiers. IEEE J. Solid-State Circuits 38, 511–520 (2003)

K.N. Leung, P.K.T. Mok, W.H. Ki, J.K.O. Sin, Three-stage large capacitive load amplifier with damping-factor-control frequency compensation. IEEE J. Solid-State Circuits 35, 221–230 (2000)

K.N. Leung, P.K.T. Mok, Nested Miller compensation in low-power CMOS design. IEEE Trans. Circuits Syst. II 48, 388–394 (2001)

X.H. Peng, W. Sansen, AC boosting compensation scheme for low-power multistage amplifiers. IEEE J. Solid-State Circuits 39, 2074–2079 (2003)

J. Ramos, X. Peng, M. Steyaert, W. Sansen, Three-stage amplifier frequency compensation, in Proc. Eur. Solid-State Circuits Conf., Lisbon, Portugal, September 2003, pp. 365–368

F. You, S.H.K. Embabi, E. Sánchez-Sinencio, Multistage amplifier topologies with nested Gm-C compensation. IEEE J. Solid-State Circuits 32, 2000–2011 (1997)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Tan, M.T., Chan, P.K., Lam, C.K. et al. AC-Boosting Frequency Compensation with Double Pole-Zero Cancellation for Multistage Amplifiers. Circuits Syst Signal Process 29, 941–951 (2010). https://doi.org/10.1007/s00034-010-9180-x

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-010-9180-x