Abstract

In this work, a novel circuit topology for a Low-Voltage Differential Signaling (LVDS) output driver with reduced power consumption is proposed. Also, a low-signal current version of the LVDS driver working with lower supply voltage is proposed along with a compatible differential current-mode receiver. Both the drivers and the receiver feature active-terminated ports that eliminate the need for a dedicated passive terminator for matching. An asymmetric impedance network on the output side of the driver selectively eliminates any reflections coming from the channel while providing a high output impedance to the outgoing signal. For a target signal swing at the receiver input, the proposed termination scheme helps to reduce the driver signal current to up to a third of the current required by a conventional LVDS driver using a passive termination at the output. The asymmetric impedance network consists of a scaled-down replica driver that drives a common drain stage acting as the load for the main driver. The proposed driver topology meeting all LVDS specifications has been implemented in 3.3-V thick-gate CMOS technology. Simulation results show an achievable data rate of 5 Gb/s while transmitting over a 7.5-in FR4 PCB backplane trace for a target BER of 10−15, with power consumption equal to 17.8 mW, which is 25% less than a conventional LVDS driver with passive source end termination producing the same voltage swing at the receiver input. The low-current version of the driver has been implemented in 0.18-μm 1.8-V digital CMOS technology and shows similar performance over the same channel with a power consumption of 4.5 mW.

Similar content being viewed by others

References

K. Abugharbieh, J. Mohan, D. Varadarajan, I. Duzevik, S. Krishnan, An ultra low power 10-Gbps LVDS output driver, in Bipolar/BiCMOS Circuits and Technology Meeting (BCTM) (2008), pp. 5–8

P.E. Allen, D.R. Holberg, CMOS Analog Circuit Design (Oxford University Press, London, 2004)

B. Razavi, Design of Integrated Circuits for Optical Communications (McGraw-Hill, New York, 2003)

A. Boni, A. Pierazzi, D. Vecchi, LVDS I/O interface for Gb/s-per-pin operation in 0.35-μm CMOS. IEEE J. Solid-State Circuits 36(4), 706–711 (2001)

M. Chen, J. Silva-Martinez, M. Nix, M.E. Robinson, Low-voltage low-power LVDS drivers. IEEE J. Solid-State Circuits, 40(2), 472–479 (2005)

W.J. Dally, J.W. Poultan, Digital Systems Engineering (Cambridge University Press, Cambridge, 1998)

M. Horowitz, C.K. Ken Yang, S. Sidiropoulos, High-speed electrical signaling: overview and limitations. IEEE MICRO 18(1), 12–24 (1998)

J.K. Kim, T.S. Kalkur, High-speed current-mode logic amplifier using positive feedback and feed-forward source-follower techniques for high-speed CMOS I/O buffer. IEEE J. Solid-State Circuits, 40(3), 796–802 (2005)

S. Kim, B.S. Kong, C.G. Lee et al., A 6-Gbps/pin half-duplex LVDS I/O for high-speed mobile DRAM, in Asian Solid State Circuits Conference (2005), pp. 53–56

LVDS Owner’s Manual Including High-Speed CML and Signal Conditioning, 4th edn. National Semiconductor Corp. (2008)

LVDS Owner’s Manual, 3 edn. National Semiconductor Corp. (2004)

G. Mandal, P. Mandal, Low power LVDS receiver for 1.3 Gbps physical layer (PHY) interface, in IEEE Intl. Symp. on Circuits and Systems (ISCAS) (2005), pp. 2180–2183

G. Mandal, P. Mandal, Low power LVDS transmitter with low common mode variation for 1-Gbps-per-pin operation, in IEEE Intl. Symp. on Circuits and Systems (ISCAS) (2004), pp. 1120–1123

P. Mandal, S. Pati, P.V.S. Rao, Active terminated differential current-mode receiver for chip-to-chip communication, in Joint IEEE North-East Workshop on Circuits and Systems and TAISA Conference (NEWCAS-TAISA) (2009), pp. 1–4

National Semiconductor Corporation, Santa Clara, USA: Channel Models (2009). www.national.com/analog

M. Oksiucik, S. Gerka, K. Baranowicz, M. Kowalewski, B. Sobala, M. Lewandowski, G. Matczak, A CMOS 0.13 micrometer realization of external component free 1-Gbps LVDS driver, in IEEE Mixed Design of Integrated Circuits and System, 22–24 June 2006. MIXDES 2006. Proceedings of the International Conference (2006), pp. 188–191

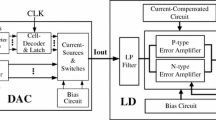

H. Ransijn, G. Salvador, D.D. Daugherty, K.D. Gaynor, II A 10-Gb/s laser/modulator driver IC with a dual-mode actively matched output buffer. IEEE J. Solid-State Circuits 36(9), 1314–1320 (2001)

P.V.S. Rao, P. Mandal, A new current-mode receiver for high-speed electrical/optical link. Int. J. Electron. Commun. (AEU) (2010). doi:10.1016/j.aeue.2010.01.018

E. Sackinger, Broadband Circuits for Optical Fiber Communication (Wiley-Interscience, New York, 2005)

A. Tajalli, Y. Leblebici, A power-efficient LVDS driver circuit in 0.18-μm technology, in Microelectronics and Electronics Conference (2007), pp. 145–148

N. Tan, S. Eriksson, Low-power chip-to-chip communication circuits. Electron. Lett. 30(21), 1732–1733 (1994)

K.L. Wong, H. Hatamkhani, M. Mansuri, C.K. Yang, A 27-mW 3.6-Gb/s I/O transceiver. IEEE J. Solid-State Circuits 39, 602–612 (2004)

Wonki-Park, Sung-Cul Lee, Design of LVDS driver based CMOS transmitter for a high speed serial link, in IEEE 2010 International Conference on Electronics and Information Engineering (ICEIE) (2010), pp. V1-302–300

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Rao, P.V.S., Desai, N. & Mandal, P. A Low-Power 5-Gb/s Current-Mode LVDS Output Driver and Receiver with Active Termination. Circuits Syst Signal Process 31, 31–49 (2012). https://doi.org/10.1007/s00034-011-9280-2

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-011-9280-2