Abstract

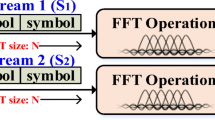

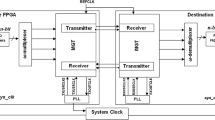

The design of Fast Fourier Transform (FFT) integrated architectures for System-on-Chip (SoC) telecom applications is addressed in this paper. After reviewing the FFT processing requirements of wireless and wired Orthogonal Frequency Division Multiplexing (OFDM) standards, including the emerging Multiple Input Multiple Output (MIMO) and OFDM Access (OFDMA) schemes, three FFT architectures are proposed: a fully parallel, a pipelined cascade and an in-place variable-size architecture, which offer different trade-offs among flexibility, processing speed and complexity. Silicon implementation results and comparisons with the state-of-the-art prove that each macrocell outperforms the known works for a target application. The fully parallel is optimized for throughput requirements up to several GSamples/s enabling Ultra-wideband (UWB) communications by using all channels foreseen in the standard. The pipelined cascade macrocell minimizes complexity for large size FFTs sustaining throughput up to 100 MSamples/s. The in-place variable-size FFT macrocell stands for its flexibility by allowing run-time reconfigurability required in OFDMA schemes while attaining the required throughput to support MIMO communications. The three architectures are also compared with common case-studies and target technology.

Similar content being viewed by others

References

P. Amirshahi, M. Navidpour, M. Kavehrad, Performance analysis of uncoded and coded OFDM broadband transmission over low voltage power-line channels with impulsive noise. IEEE Trans. Power Deliv. 21(4), 1927–1934 (2006)

J.G. Andrews, A. Ghosh, R. Muhamed, Fundamentals of WiMAX, Understanding Broadband Wireless Networking. Prentice Hall Communications Engineering and Emerging Technologies Series (Prentice Hall, New York, 2007)

F. Baronti et al., Design and verification of hardware building blocks for high-speed and fault-tolerant in-vehicle networks. IEEE Trans. Ind. Electron. 58(3), 792–801 (2011)

G. Bi, E. Jones, A pipelined FFT processor for word-sequential data. IEEE Trans. Acoust. Speech Signal Process. 37(12), 1982–1985 (1988)

J. Bingham, Multicarrier modulation for data transmission: an idea whose time has come. IEEE Commun. Mag. 28(5) (1990)

R. Cabral, S. Escarigo, H. Neto, H. Sarmento, Implementation of a DAB receiver with FPGA technology, in Proc. IEEE ICCE, Jan 2006, pp. 397–398

A. Chimenti et al., VLSI architecture for a low-power video codec system. Microelectron. J., 33(5–6), 417–427 (2002)

J.W. Cooley, J.W. Tukey, An algorithm for the machine calculation of complex Fourier series. IEEE Trans. Electron. Comput. EC-15(4), 680–681 (1966)

A.R. Cooper, Parallel architecture modified booth multiplier. IEE Proc. G, Electron. Circuits Syst. 135, 125–128 (1988)

A. Cortes, I. Velez, J. Sevillano, A. Irizar, An FFT core for DVB-T/DVB-H receivers, in Proc. Third IEEE International Conference on Electronics, Circuits, and Systems (ICECS), Dec 2006, pp. 102–105

M. Deinzer, M. Stoger, Integrated PLC-modem based on OFDM, in Int. Sym. On Power-line Communications and its Applications (ISPLC’99) (1999)

C. Del-Toso, M. Nava, A short overview of the VDSL system requirements. IEEE Commun. Mag., 40(12), 82–90 (2002)

P. Duhamel, M. Vetterli, Fast Fourier transforms: a tutorial review and a state of the art. Signal Process. 19(4), 259–299 (1990)

L. Fanucci et al., A parametric VLSI architecture for video motion estimation. Integration 31(1), 79–100 (2001)

L. Fanucci et al., Parametrized and reusable VLSI macrocells for the low-power realization of 2-D discrete-cosine-transform. Microelectron. J. 32(12), 1035–1045 (2001)

L. Fanucci et al., Power optimization of an 8051-compliant microcontroller. IEICE Trans. Electron. 88(4), 597–600 (2005)

B. Farahani, M. Ismail, WiMAX/WLAN radio receiver architecture for convergence in WMANS, in IEEE 48th Midwest Symposium on Circuits and Systems, Aug 2005, pp. 1621–1624

High rate ultra wideband PHY and MAC standard, Dec 2005, standard ECMA-368

H. Holma, A. Toskala, LTE for UMTS, OFDMA and SC-FDMA Based Radio Access (Wiley, New York, 2009)

IEEE 802.11-05/1102r4, IEEE P802.11 Wireless LANs Joint Proposal: High throughput extension to the 802.11 Standard: PHY, Jan 2006

Y. Jung, J. Kim, S. Lee, H. Yoon, J. Kim, Design and implementation of MIMO-OFDM baseband processor for high-speed wireless LANs. IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process., 54(7), 631–635 (2007)

M. Kornfeld, DVB-H—the emerging standard for mobile data communication, in IEEE International Symposium on Consumer Electronics, Sept. 2004, pp. 193–198

J. Lee, J. Moon, K. Heo, M. Sunwoo, S. Oh, I. Kim, Implementation of application-specific DSP for OFDM systems, in Proc. IEEE International Conference on Circuits and Systems (ISCAS), May 2004, vol. 3, pp. 665–668

X. Li, Z. Lai, J. Cui, A low power and small area FFT processor for OFDM. IEEE Trans. Consum. Electron., 53(2), 274–277 (2007)

Y.-W. Lin, C.-Y. Lee, Design of an FFT/IFFT processor for MIMO OFDM systems. IEEE Trans. Circuits Syst. I, 54(4), 807–815 (2007)

N. L’insalata et al., Automatic synthesis of cost effective FFT/IFFT cores for VLSI OFDM systems. IEICE Trans. Electron., E91-C(4), 487–496 (2008)

K. Nakos, D. Reisis, N. Vlassopoulos, Addressing technique for parallel memory accessing in Radix-2 FFT Processors, in IEEE Int. Conference on Electronics, Circuits and Systems (ICECS), Sep 2008, pp. 52–56

S. Oraintara, Y.J. Chen, T.Q. Nguyen, Integer Fast Fourier Transform. IEEE Trans. Signal Process. 50(3), 607–618 (2002)

S. Perels, D. Haene, P. Luethi, A. Burg, N. Felber, W. Fichtner, H. Bolcskei, ASIC implementation of a MIMO OFDM transceiver for 192 Mbps WLAN, in Proc. IEEE ESSCIRC2005 (2005)

K. Prakash, M.M. Rao, Fixed-point error analysis of radix-4 fht algorithm with optimised scaling schemes. IEE Proc., Vis. Image Signal Process. 142, 65–70 (1995)

S. Saponara, L. Fanucci, VLSI design investigation for low-cost, low-power FFT/IFFT processing in advanced VDSL transceivers. Microelectron. J. 34(2), 133–148 (2003)

S. Saponara, K. Denolf, G. Lafruit, C. Blanch, J. Bormans, Performance and complexity co-evaluation of the advanced video coding standard for cost-effective multimedia communications. EURASIP J. Appl. Signal Process. 2004(2), 220–235 (2004)

S. Saponara, L. Fanucci, S. Marsi, G. Ramponi, Algorithmic and architectural design for real-time and power-efficient Retinex image/video processing. J. Real-Time Image Process. 1(4), 267–283 (2007)

S. Saponara, L. Fanucci, S. Marsi, G. Ramponi, D. Kammler, E. Witte, Application-specific instruction-set processor for retinex-like image and video processing. IEEE Trans. Circuits Syst. II, Analog Digit. Signal Process. 54(7), 596–600 (2007)

S. Saponara, L. Fanucci, P. Terreni, Architectural-level power optimization of microcontroller cores in embedded systems. IEEE Trans. Ind. Electron. 54(1), 680–683 (2007)

S. Saponara, P. Nuzzo, C. Nani, G. Van der Plas, L. Fanucci, Architectural exploration and design of time-interleaved SAR arrays for low-power and high speed A/D converters. IEICE Trans. Electron. 92-C(6), 843–851 (2009)

R.S. Sherrat, O. Cadenas, N. Goswami, A low clock frequency FFT core implementation for multiband full-rate ultra-wideband (UWB) receivers. IEEE Trans. Consum. Electron. 51(3), 798–802 (2005)

D. Skellern, A high-speed wireless LAN. IEEE MICRO 17(1), 40–47 (1997)

C.D. Thompson, Fourier transform in VLSI. IEEE Trans. Comput. C-32(11), 1047–1057 (1983)

F. Vitullo et al., Low-complexity link microarchitecture for mesochronous communication in Networks-on-Chip. IEEE Trans. Comput. 57(9), 1196–1201 (2008)

J. Walko, Click here for VDSL2. Commun. Eng. 3(4), 9–12 (2005)

C.-C. Wang, J.-M. Huang, H.-C. Cheng, A 2K/8K mode small-area FFT processor for OFDM demodulation of DVB-T receivers. IEEE Trans. Consum. Electron. 51(1), 28–32 (2005)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Saponara, S., Rovini, M., Fanucci, L. et al. Design and Comparison of FFT VLSI Architectures for SoC Telecom Applications with Different Flexibility, Speed and Complexity Trade-Offs. Circuits Syst Signal Process 31, 627–649 (2012). https://doi.org/10.1007/s00034-011-9332-7

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-011-9332-7