Abstract

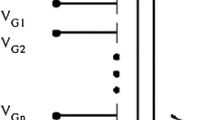

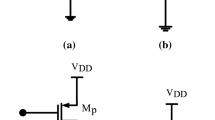

A novel bias scheme for realizing low-voltage second-order translinear loops is introduced in this paper. The provided design examples include current geometric-mean, squarer/divider, and multiplier/divider cells. The performed comparison shows that the derived analog signal processing blocks offer reduced circuit complexity and improved performance, compared with the corresponding already published counterparts.

Similar content being viewed by others

References

R.G. Carvajal, J. Ramirez-Angulo, A. Lopez-Martin, A. Torralba, J.A.G. Galan, A. Carlosena, F.M. Chavero, The flipped voltage follower: a useful cell for low-voltage low-power circuit design. IEEE Trans. Circuits Syst.-I 52, 1276–1290 (2005)

C.A. De la Cruz-Blas, A. Lopez-Martin, A. Carlosena, 1.5V MOS translinear loops with improved dynamic range and their applications to current-mode signal processing. IEEE Trans. Circuits Syst.-II 50, 918–927 (2003)

C.A. De la Cruz-Blas, A. Lopez-Martin, A. Carlosena, J. Ramirez-Angulo, Low-voltage MOS translinear analog signal processing. Circuits Syst. Signal Process. 28, 795–804 (2009)

A.J. Lopez-Martin, A. Carlosena, J. Ramirez-Angulo, Very low-voltage MOS translinear loops based on flipped voltage followers. Analog Integr. Circuits Signal Process. 40, 71–74 (2004)

E. Seevinck, R.J. Wiegerink, Generalized translinear principle. IEEE J. Solid-State Circuits 26, 1098–1102 (1991)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Psychalinos, C., Laoudias, C. Low-voltage reduced complexity cells for MOS translinear loops. Circuits Syst Signal Process 32, 2445–2456 (2013). https://doi.org/10.1007/s00034-013-9567-6

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-013-9567-6