Abstract

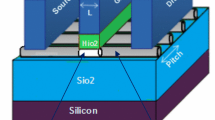

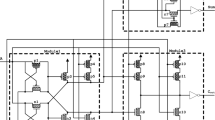

This paper presents two asymmetric and symmetric multi-threshold, high-speed, and energy-efficient Full Adder cells using Carbon Nanotube Field Effect Transistors (CNFETs). The utilization of unique properties to CNFETs to build structures inaccessible to MOSFETs technology is also evoked, particularly due to geometry-dependent threshold voltages (\(V_\mathrm{{th}} )\) in multiple-\(V_\mathrm{{th}} \) designs to achieve high-performance circuits. In order to evaluate the proposed designs, computer simulations are carried out using 32 nm-CMOS and 32 nm-CNFET technologies. Comprehensive experiments are performed to evaluate the performance of the proposed designs using different low voltage power supplies, load capacitors, frequencies, and temperatures. Simulation results demonstrate the superiority of the proposed designs in terms of delay and power-delay product compared to the other classical and state-of-the-art CMOS and CNFET-based Full Adder cells. Moreover, in order to evaluate the robustness of the proposed symmetric cell against the variations and mismatches of both diameter of the CNTs and capacitance of input capacitors, Monte Carlo transient analysis has been carried out. Simulation results confirm that the proposed cell is robust against the mentioned fluctuations.

Similar content being viewed by others

References

M. Bagherizadeh, M. Eshghi, Two novel low-power and high-speed dynamic carbon nanotube full-adder cells. Nanoscale Res. Lett. 6(519), 1–7 (2011)

M. Budnik, A. Raychowdhury, A. Bansal, K. Roy, A high density, carbon nanotube capacitor for decoupling applications, in Proc. 43rd Annual Design Automation Conference (DAC), San Francisco, CA, pp. 935–938 (2006)

C.H. Chang, J. Gu, M. Zhang, A review of 0.18-\(\mu {\rm {m}}\) full adder performances for tree structured arithmetic circuits. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 13(6), 686–695 (2005)

G. Cho, Y.B. Kim, F. Lombardi, Assessment of CNTFET based circuit performance and robustness to PVT variations, in Proc. 52nd IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), Cancun, Mexico, pp. 1106–1109 (2009)

G. Cho, Y.B. Kim, F. Lombardi, M. Choi, Performance evaluation of CNFET-based logic gates. in IEEE International Instrumentation and Measurement Technology Conference (I2MTC), Singapore, pp. 909–912 (2009)

C.J. Clement Singh, S.K. Sarkar, A.K. Biswas, Implementation of 4-bit reversible parallel adder using nanoelectronic single-electron circuitry. J. Nanoelectron. Optoelectron. 4(3), 362–369 (2009)

J. Deng, C. Chen, Hybrid CMOS-SET arithmetic circuit design using Coulomb blockade oscillation characteristic. J. Comput. Theor. Nanosci. 8(8), 1520–1526 (2011)

J. Deng, H.S.P. Wong, A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application-part I: model of the intrinsic channel region. IEEE Trans. Electron. Dev. 54(12), 3186–3194 (2007)

J. Deng, H.S.P. Wong, A compact SPICE model for carbon-nanotube field-effect transistors including nonidealities and its application-part II: full device model and circuit performance benchmarking. IEEE Trans. Electron. Dev. 54(12), 3195–3205 (2007)

K. El-Shabrawy, K. Maharatna, D. Bagnall, B.M. Al-Hashimi, Modeling SWCNT bandgap and effective mass variation using a Monte Carlo approach. IEEE Trans. Nanotechnol. 9(2), 184–193 (2010)

M. Ghadiry, M. Nadi, A. KhariA’Ain, Discrepant low PDP 8-Bit adder. Circ. Syst. Signal Process. 32(1), 1–14 (2013)

J. Guo, S. Datta, M. Lundstrom, A numerical study of scaling issues for Schottky barrier carbon nanotube transistors. Phys. Rev. B, 68, 125409 (2003)

J. Guo, A. Javey, H. Dai, S. Datta, M. Lundstrom, Predicted performance advantages of carbon nanotube transistors with doped nanotubes as source/drain. Phys. Rev. B, 309, 39 (2003)

O. Kavehei, M. Rahimi Azghadi, K. Navi, A.P. Mirbaha, Design of robust and high-performance 1-Bit CMOS full adder for nanometer design, IEEE Computer Society Annual Symposium on VLSI (ISVLSI), Montpellier, France, pp. 10–15 (2008)

A. Khatir, S. Abdolahzadegan, I. Mahmoudi, High speed multiple valued logic full adder using carbon nanotube field effect transistor. Int. J. VLSI Design Commun. Syst. (VLSICS) 2(1), 1–9 (2011)

Y.B. Kim, Y.B. Kim, F. Lombardi, A novel design methodology to optimize the speed and power of the CNTFET circuits, in Proc. 52nd IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), Cancun, Mexico, pp. 1130–1133 (2009)

S. Lin, Y.B. Kim, F. Lombardi, A novel CNFET based ternary logic gate design, in Proc. 52nd IEEE International Midwest Symposium on Circuits and Systems (MWSCAS), Cancun, Mexico, pp. 435–438 (2009)

S. Lin, Y.B. Kim, F. Lombardi, CNTFET-based design of ternary logic gates and arithmetic circuits. IEEE Trans. Nanotechnol. 10(2), 217–225 (2011)

S. Lin, Y.B. Kim, F. Lombardi, Y.J. Lee, A new SRAM cell design using CNTFETs. IEEE International SOC Design Conference (ISOCC), Busan, Korea, pp. 168–171 (2008)

M.H. Moaiyeri, R. Chavoshisani, A. Jalali, K. Navi, O. Hashemipour, High-performance mixed-mode universal min–max circuits for nanotechnology. Circ. Syst. Signal Process. 31(2), 465–488 (2012)

M.H. Moaiyeri, K. Navi, O. Hashemipour, Design and evaluation of CNFET-based quaternary circuits. Circ. Syst. Signal Process. 31(5), 1631–1652 (2012)

K. Navi, R. Sharifi Rad, A low-voltage and energy-efficient full adder cell based on carbon nanotube technology. Nano-Micro Lett. 2(2), 114–120 (2010)

K. Navi, V. Foroutan, M. Rahimi Azghadi, M. Maeen, M. Ebrahimpour, M. Kaveh, A. Kavehei, A novel low-power full-adder cell with new technique in designing logical gates based on static CMOS inverter. Microelectron. J. 40(10), 1441–1448 (2009)

K. Navi, A. Momeni, F. Sharifi, P. Keshavarzian, Two novel ultra high speed carbon nanotube full-adder cells. IEICE Electron. express 6(19), 1395–1401 (2009)

K. Navi, S. Sayedsalehi, R. Farazkish, M. Rahimi Azghadi, Five-input majority gate, a new device for quantum-dot cellular automata. J. Comput. Theor. Nanosci. 7(8), 1546–1553 (2010)

N. Patil, A. Lin, J. Zhang, H. Wei, K. Anderson, H.S.P. Wong, S. Mitra, Scalable carbon nanotube computational and storage circuits immune to metallic and mispositioned carbon nanotubes. IEEE Trans. Nanotechnol. 10(4), 744–750 (2011)

W. Porod, C. Lent, G.H. Bernstein, A.O. Orlov, I. Hamlani, G.L. Snider, J.L. Merz, Quantum-dot cellular automata: computing with coupled quantum dots. Int. J. Electron. 86(5), 549–590 (1999)

Predictive Technology Model, http://ptm.asu.edu. Accessed 15 July 2012

A. Raychowdhury, K. Roy, Carbon-nanotube-based voltage-mode multiple-valued logic design. IEEE Trans. Nanotechnol. 4(2), 168–179 (2005)

A. Raychowdhury, K. Roy, Carbon nanotube electronics: design of high-performance and low-power digital circuits. IEEE Trans. Circ. Syst. I Reg. Papers 54(11), 2391–2401 (2007)

M.R. Reshadinezhad, M.H. Moaiyeri, K. Navi, An energy-efficient full adder cell using CNFET technology. IEICE Trans. Electron. E95-c(4), 744–751 (2012)

H. Shahidipour, A. Ahmadi, K. Maharatna, Effect of variability in SWCNT-based logic gates, in International Symposium on Integrated Circuits (ISIC), Singapore, pp. 252–255 (2009)

A.M. Shams, T.K. Darwish, M.A. Bayoumi, Performance analysis of low-power 1-Bit CMOS full adder cells. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 10(1), 20–29 (2002)

N. Weste, K. Eshraghian, Principles of CMOS VLSI Design: A system Perspective (Addison-Wesley, Reading, MA, 1993)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Safaei Mehrabani, Y., Eshghi, M. A Symmetric, Multi-Threshold, High-Speed and Efficient-Energy 1-Bit Full Adder Cell Design Using CNFET Technology. Circuits Syst Signal Process 34, 739–759 (2015). https://doi.org/10.1007/s00034-014-9887-1

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-014-9887-1