Abstract

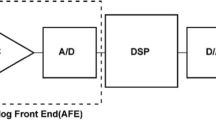

In this paper a low power, high performance analog front-end (AFE) circuit for digital hearing aid SoC is presented. It adopts digital-feedback-gain-control (DFGC) for accurate amplification and the multi-bit Sigma–Delta modulator technique to improve dynamic range with low power consumption. The auto gain control loop with peak-statistics-logic and DFGC can also work in variable gain control mode controlled by digital signal processor. Moreover, data weighted averaging circuit reduces nonlinearity of multi-bit Sigma–Delta technique. The analog front-end is implemented in SMIC 0.13 \(\upmu \)m 1P8M CMOS process. The measurement results show that in 1 V power supply, at 200 mV\(_{\mathrm{p-p}}\), between 100 Hz and 8 kHz, the output minimum noise floor is \(-\)120 dBm. And the maximal SNR is 88 dB, SNDR is 81 dB, total power is 180 \(\upmu \)W for a single-channel AFE, which meets the application requirement of hearing aid SoC.

Similar content being viewed by others

References

W.M. Baker, R. Sarpeshkar, Low-power single-loop and dual-loop AGCs for bionic ears. IEEE J. Solid-State Circuit 41(9), 1983–1990 (2006)

L.D. Huei, K.T. Haur, Advancing data weighted averaging technique for multi-bit Sigma–Delta modulators. IEEE Trans. Circuits Syst. 4(10), 838–842 (2007)

S. Kim, J.Y. Lee, S.J. Song, An energy-efficient analog front-end circuit for a sub-1V digital hearing aid. IEEE J. Solid-State Circuit 41(4), 876–882 (2006)

S. Kim, J.Y. Lee, J.C. Nam, A full integrated digital hearing aid chip with human factor considerations. IEEE J. Solid-State Circuit 43(1), 266–274 (2008)

M. Matthew, P. Craig, A multibit Sigma–Delta ADC for multimode receivers. IEEE J. Solid-State Circuits 38(3), 475–482 (2003)

H. Nerteboom., M.A. Janssens et al. A single battery 0.9 V-operated digital sound processing IC including AD/DA and IR receiver with 2 mW power consumption. IEEE international solid-state circuit conference digest of technical paper (Feb 1997), p. 98

V. Peluso, P. Vancorenland, A.M. Marques, M.S.J. Steyaert, W. Sansen, A 900-mV low-power A/D converter with 77-dB dynamic range. IEEE J. Solid-State Circuits 33(12), 1887–1897 (1998)

G.F. Serra, J.L. Huertas, Low voltage CMOS sub threshold log amplification and AGC. IEEE Proc. Circuit Dev. Syst. 52(1), 61–70 (2005)

M.J. Silva, B.S. Solis, M. Schellenberg, A CMOS hearing aid device. Analog Integr. Circuit Signal Process. 21(2), 163–168 (1999)

A. Sukumaran, K. Karanjkar, S. Jhanwar. A 1.2 V 285 \(\mu \) A analog front end chip for a digital hearing aid in 0.13 \(\mu \) m CMOS. in IEEE Asian Solid-State Circuits Conference (A-SSCC) (2013), p. 397

D. Wayne, M. Rives, T. Huynh, D. Preves, J. Newton, A Single-Chip Hearing Aid with One Volt Switched-Capacitor Filters. in Proceedings IEEE Custom Integrated Circuits Conference (1992), p. 751

G. Yves, S. Michel, S. Willy, A high-performance multibit \(\Delta \Sigma \) CMOS ADC. IEEE J. Solid-State Circuits 35(12), 1829–1840 (2000)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Chen, C., Fan, J., Hu, X. et al. A Low Power, High Performance Analog Front-End Circuit for 1 V Digital Hearing Aid SoC. Circuits Syst Signal Process 34, 1391–1404 (2015). https://doi.org/10.1007/s00034-014-9907-1

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-014-9907-1