Abstract

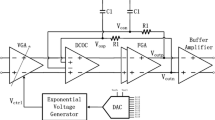

The noise contribution of a DC offset cancelation (DCOC) circuit in a programmable gain amplifier (PGA) is studied for the first time in this paper. The analysis presented shows that the DCOC-induced noise may deteriorate the PGA’s noise performance significantly if we do not pay enough attention to it. For an analog DCOC (ADCOC), it is concluded that the PGA’s noise increases rapidly as the output DC offset decreases, thereby causing difficulties to achieve both low noise and low DC offset simultaneously. We propose an optimization technique that can effectively alleviate the noise issue by increasing the feedback amplifier’s gain and the resistor’s value simultaneously, while maintaining a reasonable DC gain. For a digital DCOC (DDCOC), the extra noise comes from the transistors of the current source (sink) bank. The transistors with a longer channel length are preferred for their lower thermal and flicker noise current. The proof-of-concept prototypes are designed in a 0.18-\(\upmu \)m CMOS process, and a 3-stage PGA with ADCOC is fabricated. The measurement results validate the analysis and simulation results well.

Similar content being viewed by others

References

A.F. Arbel, Comparison between the noise performance of current-mode and voltage-mode amplifiers. Analog Integr. Circuits Signal Process. 7, 221–242 (1995)

M. Balsi, F. Centurelli, A. Pallotta et al., Input-matching and offset-cancelling networks for limiting amplifiers in optical communication systems. Analog Integr. Circuits Signal Process. 47, 23–32 (2006)

B. Calvo, S. Celma, M.T. Sanz, Low-voltage low-power 100 MHz programmable gain amplifier in 0.35 \(\mu \)m CMOS. Analog Integr. Circuits Signal Process. 48, 263–266 (2006)

J. Chang, A.A. Abidi, C.R. Viswanathan, Flicker noise in CMOS transistors from subthreshold to strong inversion at various temperatures. IEEE Trans. Electron Devices 41, 1965–1971 (1994)

Z.S. Cheng, J.C. Bor, A CMOS variable gain amplifier with DC offset calibration loop for wireless communications. (IEEE International Symposium on VLSI Design, Automation and Test, pp. 1–4 (2006)

S. D’Amico, A. Baschirotto, K. Philips, et al., A 240MHz programmable gain amplifier & filter for ultra low power low-rate UWB receivers. Proceedings of IEEE on ESSCIRC, pp. 260–263 (2009)

H. Elwan, A.M. Soliman, M. Ismail, A CMOS Norton amplifier-based digitally controlled VGA for low-power wireless applications. IEEE Trans. Circuits Syst. II Analog Digit. Signal Process. 48(3), 245–254 (2001)

H. Elwan, A. Tekin, K. Pedrotti, A differential-ramp based 65 dB-linear VGA technique in 65 nm CMOS. IEEE J. Solid–State Circuits 44(9), 2503–2514 (2009)

Z. Gong, X. Chu, Q. Lei et al., CMOS analog baseband circuitry for an IEEE 802.11 b/g/n WLAN transceiver. J. Semicond. 32(11), 115001 (2012)

C. Guo, H.C. Luong, A 70-MHz 70-dB-gain VGA with automatic continuous-time offset cancellation. IEEE Proceedings of the 43rd Midwest Symposium on Circuits and Systems, pp. 306–309 (2000)

R.G. Jensen, K.T. Christensen, E. Bruun, Programmable baseband filter for multistandard mobile phones. Analog Integr. Circuits Signal Process. 34, 49–57 (2003)

S.Y. Kang, J. Jang, I.Y. Oh et al., A 2.16 mW low power digitally-controlled variable gain amplifier. Microw. Wirel. Compon. Lett. IEEE 20(3), 172–174 (2010)

R. Kitamura, T. Tsukizawa, N. Saito, An 84 dB-gain-range and 1 GHz-bandwidth variable gain amplifier using gain flattening capacitors for multi-gigabit radio. IEEE Radio and Wireless Symposium (RWS), pp. 220–222 (2013)

S. Koziel, Noise analysis and optimization of continuous-time active-RC filters. Proceedings of the 11th IEEE International Conference on Electronics, Circuits and Systems, pp. 45–48 (2004)

T.B. Kumar, K. Ma, K.S. Yeo, Temperature-compensated dB-linear digitally controlled variable gain amplifier with DC offset cancellation. IEEE Trans. Microw Theory Tech. 61(7), 2648–2661 (2013)

S. Li, J. Li, X. Gu, H. Wang, A continuously and widely tunable analog baseband chain with digital-assisted calibration for multi-standard DBS applications. J. Semicond. 34(6), 143–151 (2013)

D. Liang, Q. Ye, A 96-dB CMOS programmable gain amplifier for Low-IF GPS receiver. IEEE International Conference on Communications, Circuits and Systems, pp. 101–104 (2008)

B.Q. Liu, B.Y. Chi, A 25-MHz bandwidth, 37-dB gain range CMOS Programmable Gain Amplifier with DC-Offset cancellation and driver buffer. IEEE 11th International Conference on Solid–State and Integrated Circuit Technology, pp. 1–3 (2012)

P.I. Mak, U. Seng-Pan, R.P. Martins, On the design of a programmable-gain amplifier with built-in compact DC-offset cancellers for very low-voltage WLAN systems. IEEE Trans. Circuits Syst. I Regul. Pap. 55(2), 496–509 (2008)

S.M. Oh, K.S. Park, H.H. Yoo, et al., A design of DC offset canceller using parallel compensation. IEEE International Symposium on Circuits and Systems, pp. 1685–1688 (2007)

D.D. Pham, J. Brinkhoff, K. Kang, et al, Feedforward technique for offset cancellation in broadband differential amplifiers. Proceedings of the 12th International Symposium on Integrated Circuits, pp. 429–432 (2009)

B. Rahmatian, S. Mirabbasi, A low-power 75dB digitally programmable CMOS variable-gain amplifier. IEEE Canadian Conference on Electrical and Computer Engineering, pp. 522–525 (2007)

B. Razavi, Design of Analog CMOS Integrated Circuits (McGraw-Hill, New York, 2001)

C.M. Ta, C.H. Yong, W.G. Yeoh, A 2.7 mW, 0.064mm\(^{2}\) linear-in-dB VGA with 60 dB tuning range, 100 MHz bandwidth, and two DC offset cancellation loops. Proceedings of IEEE International Workshop on Radio-Frequency Integration Technology, pp. 74–77 (2005)

Y. Tsividis, Operation and Modeling of the MOS Transistor (McGraw-Hill, New York, 1987)

S.C. Tsou, C.F. Li, P.C. Huang, A low-power CMOS linear-in-decibel variable gain amplifier with programmable bandwidth and stable group delay. IEEE Trans. Circuits Syst. II Exp. Br. 53(12), 1436–1440 (2006)

T. Yasuda, H. Andoh, Differential analog data path DC offset calibration methods. Analog Integr. Circuits Signal Process. 27, 245–251 (2000)

Acknowledgments

This work was partially supported by the National Natural Science Foundation of China (Nos. 61306069, 61106024). The authors wish to thank Wei Li and Li Zhang for technical instructions. The authors are also gratefully acknowledge the helpful comments and suggestions of the reviewers, which have improved the presentation.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Ma, L., Wang, Z., Xu, J. et al. Noise Analysis and Optimization of Programmable Gain Amplifier with DC Offset Cancelation. Circuits Syst Signal Process 35, 753–770 (2016). https://doi.org/10.1007/s00034-015-0093-6

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-015-0093-6