Abstract

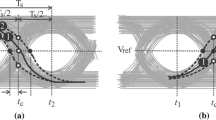

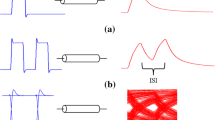

This paper presents an adaptive decision feedback equalizer (DFE) utilizing a hexagon eye-opening monitor to detect both the violation of the minimum eye and the severity of the violation so as to allow different step sizes to be used in search for optimal DFE tap coefficients. In addition, a new slope detection method is used to detect the deviation of received data symbols from the desired one so as to guide the direction of search for the optimal DFE tap coefficients. The proposed adaptive DFE allows designers to freely set DFE constraints such as the minimum vertical eye opening, the minimum horizontal eye opening, and the maximum jitter of the sampling clock so as to address the needs of different applications. To validate its effectiveness, the proposed adaptive DFE is embedded in a 2 Gbps serial link designed in an IBM 130 nm 1.2 V CMOS technology. The link is analyzed using Spectre from Cadence Design Systems with BSIM4 device models. Simulation results demonstrate that the proposed adaptive DFE is capable of opening completely closed data eyes at the far end of a 2-m FR4 channel with 75 % vertical eye opening, 78 % horizontal eye opening, and 21 % data jitter while consuming 17.38 mW.

Similar content being viewed by others

References

B. Abiri, A. Sheikholeslami, H. Tamura, M. Kibune, An adaptation engine for a \(2\times \) blind ADC-based CDR in 65 nm CMOS. IEEE J. Solid State Circuits 46(12), 3140–3149 (2011)

A. Al-Taee, F. Yuan, A. Ye, S. Sadr, New 2D eye-opening monitor for Gbps serial links. IEEE Trans. VLSI Syst. 22(6), 1209–1218 (2014)

M. Austin, Decision-feedback equalization for digital communication over dispersive channels. IEEE Int’l Research Laboratory of Electronics Technical Report 461 (1967)

D. Bhatta, K. Kim, E. Gebara, J. Laskar, A 10 Gb/s two dimensional scanning eye opening monitor in \(0.18\,\upmu {\rm m}\) CMOS process. In Proceedings of IEEE Int’l Microwave Symposium on Digest (2009), pp. 1141–1144

H. Cui, J. Lee, S. Jeon, S. Bae, Y. Sohn, J. Sim, H. Park, A single-loop SS-LMS algorithm with single-ended integrating DFE receiver for multi-drop DRAM interface. IEEE J. Solid State Circuits 46(9), 2053–2063 (2011)

T. Carusone, D. Johns, K. Martin, Analog Integrated Circuit Design, 2nd edn. (Wiley, New York, 2012)

A. Fayed, M. Ismail, A low-voltage, low-power CMOS analog adaptive equalizer for UTP-5 cables. IEEE Trans. Circuits Syst. I. 55(2), 480–495 (2008)

F. Gerfers, G. Besten, P. Petkov, J. Conder, A. Koellmann, A 0.2–2 Gb/s \(6\times \) OSR receiver using a digitally self-adaptive equalizer. IEEE J. Solid State Circuits 43(6), 1436–1448 (2008)

B. Kim, Y. Liu, T. Dickson, J. Bulzacchelli, D. Friedman, A 10-Gb/s compact low-power serial I/O with DFE–IIR equalization in 65-nm CMOS. IEEE J. Solid State Circuits 44(12), 3526–3538 (2009)

Y. Hidaka, W. Gai, T. Horie, J. Jiang, Y. Koyanagi, H. Osone, A 4-channel 1.25–10.3 Gb/s backplane transceiver macro with 35 dB equalizer and sign-based zero-forcing adaptive control. IEEE J. Solid State Circuits 44(12), 3547–3559 (2009)

K. Krishna, D. Yokoyama-Martin, A. Caffee, C. Jones, M. Loikkanen, J. Parker, R. Segelken, J. Sonntag, J. Stonick, S. Titus, D. Weinlader, S. Wolfer, A multi-giga-bit backplane transceiver core in 0.13-m CMOS with a power-efficient equalization architecture. IEEE J. Solid State Circuits 40(12), 26582666 (2005)

M. Pozzoni, S. Erba, P. Viola, M. Pisati, E. Depaoli, D. Sanzogni, R. Brama, D. Baldi, M. Repossi, F. Svelto, A multi-standard 1.5 to 10 Gb/s latch-based 3-tap DFE receiver with a SSC tolerant CDR for serial backplane communication. IEEE J. Solid State Circuits 44(4), 1306–1315 (2009)

S. Shahramian, H. Yasotharan, A. Carusone, Decision feedback equalizer architectures with multiple continuous-time infinite impulse response filters. IEEE Trans. Circuits Syst. II 59(6), 226–230 (2012)

J. Winters, R. Gitlin, Electrical signal processing techniques in long-haul fiber-optic systems. IEEE Trans. Commun. 38(9), 1439–1453 (1990)

K. Wong, E. Chen, C. Yang, Edge and data adaptive equalization of serial-link transceivers. IEEE J. Solid State Circuits 43(9), 2157–2169 (2008)

F. Yuan, A. Al-Taee, A. Ye, S. Sadr, Design techniques for decision feedback equalization of multi-Gbps serial data links: a state-of-the-art review. IET Circuits Devices Syst. 8(2), 118–130 (2014)

Acknowledgments

Financial support from the Natural Science and Engineering Research Council (NSERC) of Canada and Ontario Graduate Scholarship (OGS) program, and computer-aided design tools from CMC Microsystems, Kingston, ON, Canada, are gratefully appreciated by the authors.

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Al-Taee, A.R., Yuan, F. & Ye, A. Adaptive Decision Feedback Equalizer with Hexagon EOM and Jitter Detection. Circuits Syst Signal Process 35, 2487–2501 (2016). https://doi.org/10.1007/s00034-015-0147-9

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-015-0147-9