Abstract

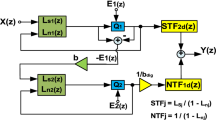

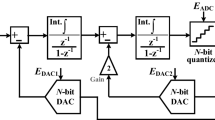

A new topology of multi-loop sigma-delta \((\Sigma \Delta )\) modulators is proposed which utilizes two analog inter-stage paths to improve the noise-shaping ability of the modulator by one order and simultaneously optimizing one pair of noise transfer function zeros. Furthermore, an improved version of this modulator is presented which is simpler to implement. So, by using minimum extra circuit and without increasing the number of active blocks, the in-band quantization noise is significantly reduced, and hence, the modulator signal-to-noise and distortion ratio (SNDR) is highly increased. As an example, a multistage noise-shaping (MASH) 2-1 \(\Sigma \Delta \) modulator based on the improved proposed structure is more examined. Some implementation considerations including the timing issue and first-stage quantization noise extraction are verified. Theoretical analysis and simulation results in both system and circuit levels are presented to confirm the usefulness of the proposed structure. The modulator is implemented in a 90-nm CMOS technology using Spectre-RF. For 10 MHz signal bandwidth, 85.2 dB SNDR and 87 dB dynamic range are achieved, while the power consumption is 31.6 mW from a single 1 V power supply.

Similar content being viewed by others

References

M. Aboudina, B. Razavi, A \(\Delta \Sigma \) CMOS ADC with 80-dB dynamic range and 31-MHz signal bandwidth, in IEEE International Midwest Symposium on Circuits and Systems (2009), pp. 397–401

R. Baird, T. Fiez, Linearity enhancement of multibit delta-sigma A/D and D/A converters using data weighted averaging. IEEE Trans. Circuits Syst. II 42(12), 753–762 (1995)

E. Bilhan, F. Maloberti, A wideband sigma-delta modulator with cross-coupled two-paths. IEEE Trans. Circuits Syst. I 56(5), 886–893 (2009)

L. Bos, G. Vandersteen, P. Rombouts, A. Geis, A. Morgado, Y. Rolain, G. Van der Plas, J. Ryckaert, Multirate cascaded discrete-time low-pass \(\Delta \Sigma \) modulator for GSM/Bluetooth/UMTS. IEEE J. Solid-State Circuits 45(6), 1198–1208 (2010)

D.P. Brown, On limit cycles of second-order sigma-delta modulators with constant input. Circuits Syst. Signal Process. 14(5), 675–688 (1995)

K. Bult, G.J. Geelen, A fast-settling CMOS op amp for SC circuits with 90-dB DC gain. IEEE J. Solid-State Circuits 25(6), 1379–1384 (1990)

F. Chen, T. Kuendiger, S. Erfani, M. Ahmadi, Design of a wideband low-power continuous-time \(\Sigma \Delta \) modulator in 90 nm CMOS technology. Analog Integr. Circuits Signal Process. 54(3), 187–199 (2008)

T.B. Cho, P.R. Gray, A 10 b, 20 Msample/s, 35 mW pipeline A/D converter. IEEE J. Solid-State Circuits 30(3), 166–172 (1995)

K. Cornelissens, M. Steyaert, Design considerations for cascade \(\Delta \Sigma \) ADCs. IEEE Trans. Circuits Syst. II 55(5), 389–393 (2008)

M. de Bock, P. Rombouts, A double-sampling cross noise-coupled split \(\Sigma \Delta \)-modulation A/D converter with 80 dB SNR, in IEEE International Conference on Electronics, Circuits and Systems (ICECS) (2009), pp. 45–48

M. Dessouky, A. Kaiser, Very low-voltage digital-audio \(\Delta \Sigma \) modulator with 88-dB dynamic range using local switch bootstrapping. IEEE J. Solid-State Circuits 36(3), 349–355 (2001)

Y. Du, T. He, Y. Jiang, S. Sin, U. Seng-Pan, R. P. Martins, A robust NTF zero optimization technique for both low and high OSRs sigma-delta modulators, in IEEE Asia Pacific Conference on Circuits and Systems (APCCAS) (2012), pp. 29–32

Y. Fujimoto, Y. Kanazawa, P. Loré, K. Iizuka, A 100 MS /s 4 MHz bandwidth 70 dB SNR \(\Delta \Sigma \) ADC in 90 nm CMOS. IEEE J. Solid-State Circuits 44(6), 1697–1708 (2009)

A.A. Hamoui, K.W. Martin, High-order multibit modulators and pseudo data-weighted-averaging in low-oversampling \(\Delta \Sigma \) ADCs for broad-band applications. IEEE Trans. Circuits Syst. I 51(1), 72–85 (2004)

C.Y. Ho, B.W. Ling, J.D. Reiss, Fuzzy impulsive control of high-order interpolative low-pass sigma-delta modulators. IEEE Trans. Circuits Syst. I 53(10), 2224–2233 (2006)

C.Y. Ho, B.W. Ling, J.D. Reiss, X. Yu, Nonlinear behaviors of bandpass sigma-delta modulators with stable system matrices. IEEE Trans. Circuits Syst. II 53(11), 1240–1244 (2006)

K.C. Hong, H. Chiueh, A 36-mW 320-MHz CMOS continuous-time sigma-delta modulator with 10-MHz bandwidth and 12-bit resolution, in IEEE International Midwest Symposium on Circuits and Systems (2010), pp. 725–728

Y. Jung, H. Roh, J. Roh, An input-feedforward multibit adder-less modulator for ultrasound imaging systems. IEEE Trans. Instrum. Meas. 62(8), 2215–2227 (2013)

B. Khazaeili, M. Yavari, MASH \(\Sigma \Delta \) modulator with highly reduced in-band quantisation noise. Electron. Lett. 50(3), 161–163 (2014)

B. Khazaeili, M. Yavari, A simple global resonation strategy for wideband discrete-time MASH \(\Sigma \Delta \) modulators, in 22nd Iranian Conference on Electrical Engineering (ICEE) (2014), pp. 334–337

K. Lee, C. Jeongseok, M. Aniya, K. Hamashita, K. Takasuka, S. Takeuchi, G.C. Temes, A noise-coupled time-interleaved \(\Delta \Sigma \) ADC with 4.2MHz BW, -98dB THD, and 79dB SNDR, in IEEE International Solid-State Circuits Conference, Digest of Technical Papers (2008), pp. 494–631

K. Lee, J. Chae, M. Aniya, K. Hamashita, K. Takasuka, S. Takeuchi, G.C. Temes, A noise-coupled time-interleaved delta-sigma ADC with 4.2 MHz bandwidth, 98 dB THD, and 79 dB SNDR. IEEE J. Solid-State Circuits 43(12), 2601–2612 (2008)

K. Lee, M.R. Miller, G.C. Temes, An 8.1 mW, 82 dB delta-sigma ADC with 1.9 MHz BW and 98 dB THD. IEEE J. Solid-State Circuits 44(8), 2202–2211 (2009)

B.W. Ling, C.Y. Ho, Q. Dai, J.D. Reiss, Reduction of quantization noise via periodic code for oversampled input signals and the corresponding optimal code design. Digit. Signal Process. 24, 209–222 (2014)

C.Y. Lu, M. Onabajo, V. Gadde, L. Yung-chung, C. Hsein-Pu, V. Periasami, J. Silva-Martinez, A 25 MHz bandwidth 5th-order continuous-time low-pass sigma-delta modulator with 67.7 dB SNDR using time-domain quantization and feedback. IEEE J. Solid-State Circuits 45(9), 1795–1808 (2010)

M.H. Maghami, M. Yavari, A hybrid CT/DT double-sampled SMASH \(\Sigma \Delta \) modulator for broadband applications in 90 nm CMOS technology. Analog Integr. Circuits Signal Process. 73(1), 101–114 (2012)

N. Maghari, S. Kwon, U.-K. Moon, 74 dB SNDR multi-loop sturdy-MASH delta-sigma modulator using 35 dB open-loop opamp gain. IEEE J. Solid-State Circuits 44(8), 2212–2221 (2009)

N. Maghari, U.-K. Moon, A third-order DT \(\Delta \Sigma \) Modulator using noise-shaped bi-directional single-slope quantizer. IEEE J. Solid-State Circuits 46(12), 2882–2891 (2011)

P. Malcovati, S. Brigati, F. Francesconi, F. Maloberti, Behavioral modeling of switched-capacitor sigma-delta modulators. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 50(3), 352–364 (2003)

P. Malla, H. Lakdawala, K. Kornegay, K. Soumyanath, A 28-mW spectrum-sensing reconfigurable 20MHz 72dB-SNR 70 dB-SNDR DT \(\Delta \Sigma \) ADC for 802.11n/WIMAX receivers, in IEEE International Solid-State Circuits Conference, Digest of Technical Papers (2008), pp. 496–631

P. Malla, H. Lakdawala, R. Naiknaware, K. Soumyanath, K. Kornegay, Systematic design of wideband \(\Delta \Sigma \) modulator for WiFi/WiMAX receivers. J. Analog Integr. Circuits Signal Process. 65(2), 197–208 (2010)

K. Matsukawa, Y. Mitani, M. Takayama, K. Obata, S. Dsho, A. Matsuzawa, A fifth-order continuous-time delta-sigma modulator with single-opamp resonator. IEEE J. Solid-State Circuits 45(4), 697–706 (2010)

X. Meng, Y. Zhang, T. He, G.C. Temes, A noise-coupled low-distortion delta-sigma ADC with shifted loop delays, in IEEE 57th International Midwest Symposium on Circuits and Systems (2014), pp. 587–590

A. Morgado, R. del Río, J. de la Rosa, Adaptive SMASH \(\Sigma \Delta \) converters for the next generation of mobile phones—design issues and practical solutions, in IEEE International Conference NEWCAS (2010), pp. 357–360

A. Morgado, R. del Río, J. de la Rosa, Resonation-based cascade \(\Sigma \Delta \) modulator for broadband low-voltage A/D conversion. Electron. Lett. 44(2), 97–99 (2008)

T. Oh, N. Maghari, U.-K. Moon, A second-order \(\Delta \Sigma \) ADC using noise-shaped two-step integrating quantizer. IEEE J. Solid-State Circuits 48(6), 1465–1474 (2013)

J. Peng, J. Wang, S. Tan, Optimal FIR filter design based on curve fitting approximation for uncertain 2–1 sigma-delta modulator. Circuits Syst. Signal Process. 33(3), 885–894 (2014)

O. Rajaee, S. Takeuch, M. Aniya, K. Hamashita, U.K. Moon, Low-OSR over-ranging hybrid ADC incorporating noise-shaped two-step quantizer. IEEE J. Solid-State Circuits 46(11), 2458–2468 (2011)

O. Rajaee, T. Musah, S. Takeuchi, M. Aniya, K. Hamashita, P. Hanumoluet, U.-K. Moon, A 79dB 80 MHz 8X-OSR hybrid delta-sigma/pipeline ADC, in Symposium on VLSI Circuits (2009), pp. 74–75

B. Razavi, B.A. Wooley, Design techniques for high-speed, high-resolution comparators. IEEE J. Solid-State Circuits 27(12), 1916–1926 (1992)

M. Sanchez-Renedo, S. Patón, L. Hernández, A 2-2 discrete time cascaded \(\Sigma \Delta \) modulator with NTF zero using interstage feedback, in IEEE International Conference on Electronics in Circuits and Systems (ICECS) (2006), pp. 954–957

C. Sandner, M. Clara, A. Santner, T. Hartig, F. Kuttner, A 6-bit 1.2-GS/s low-power flash-ADC in 0.13-\(\mu \)m digital CMOS. IEEE J. Solid-State Circuits 40(7), 1499–1505 (2005)

R. Schoofs, M.S.J. Steyaert, W. Sansen, A design-optimized continuous-time delta–sigma ADC for WLAN applications. IEEE Trans. Circuits Syst. I Regul. Pap. 54(1), 209–217 (2007)

R. Schreier, G.C. Temes, Understanding delta-sigma data converters (Wiley/IEEE Press, Piscataway, 2005)

B.H. Seyedhosseinzadeh, M. Yavari, An efficient low-power sigma-delta modulator for multi-standard wireless applications. J. Circuits Syst. Comput. 21(04), 1250028 (2012)

J. Silva, U. Moon, J. Steensgaard, G.C. Temes, Wideband low-distortion delta-sigma ADC topology. Electron. Lett. 37(12), 737–738 (2001)

Z. Sohrabi, M. Yavari, A 13 bit 10 MHz bandwidth MASH 3–2 \(\Sigma \Delta \) modulator in 90 nm CMOS. Int. J. Circuit Theory Appl. 41(11), 1136–1153 (2012)

G.C. Temes, New architectures for low-power delta-sigma analog-to-digital converter, in IEEE Asia Pacific Conference on Circuits and Systems (2008), pp. 1–6

A.H.M. Vanruermund, H. Casier, M. Steyaert, Analog Circuit Design (Springer, New York, 2006)

K. Vleugels, S. Rabii, B.A. Wooley, A 2.5-V sigma-delta modulator for broadband communications applications. IEEE J. Solid-State Circuits 36(12), 1887–1899 (2001)

R.H. Walden, Analog-to-digital converter survey and analysis. IEEE J. Sel. Areas Commun. 17(4), 539–550 (1999)

K. Yamamoto, A.C. Carusone, A 1-1-1-1 MASH delta-sigma modulator with dynamic comparator-based OTAs. IEEE J. Solid-State Circuits 47(8), 1866–1883 (2012)

X. Yang, H. Zhang, G. Chen, A low-power second-order two-channel time-interleaved \(\Sigma \Delta \) modulator for broadband application. Inst. Electron. Inf. Commun. Eng (IEICE) Trans. Electron. 92(6), 852–859 (2009)

F. Yang, M. Gani, Robust H2 approach for digital correction of cascaded Sigma Delta modulator. Circuits Syst. Signal Process. 26(4), 607–618 (2007)

M. Yavari, O. Shoaei, A. Rodriguez-Vazquez, Systematic and optimal design of CMOS two-stage opamps with hybrid cascode compensation, in Proceedings on Design, Automation and Test in Europe (2006), pp. 144–149

M. Yavari, O. Shoaei, Low-voltage low-power fast-settling CMOS operational transconductance amplifiers for switched-capacitor applications. IEE Proc. Circuits Devices Syst. 151(6), 573–578 (2004)

A. Yukawa, A CMOS 8-bit high-speed A/D converter IC. IEEE J. Solid-State Circuits 20(3), 775–779 (1985)

R. Zanbaghi, S. Saxena, G.C. Temes, T.S. Feiz, A 75-dB SNDR, 5-MHz bandwidth stage-shared 2–2 MASH modulator dissipating 16 mW power. IEEE Trans. Circuits Syst. I 59(8), 1614–1625 (2012)

R. Zanbaghi, T.S. Fiez, G. Temes, A new zero-optimization scheme for noise-coupled \(\Delta \Sigma \) ADCs, in IEEE International Symposium on Circuits and Systems (2010), pp. 2163–2166

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Khazaeili, B., Yavari, M. A Simple Structure for MASH \(\Sigma \Delta \) Modulators with Highly Reduced In-Band Quantization Noise. Circuits Syst Signal Process 36, 2125–2153 (2017). https://doi.org/10.1007/s00034-016-0406-4

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-016-0406-4