Abstract

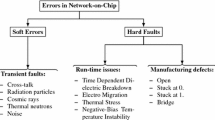

System-on-ship (SoC) design in the nanoelectronics era brings us not only many opportunities but also several challenges like synchronization, process uncertainty, global interconnecting delay, high scalability, and reliability. Network on Chip (NoC) could be a communication subsystem and it is rising as a revolutionary design methodology to solve the problems associated with SoC designing. Reliability is one of the major designing challenges in NoC design under technology limitations at low voltage operations and under the influence of very deep sub-micron noise sources, including crosstalk noise. To achieve the reliability of NoC, error controlling codes (ECC) are required. ECCs are broadly categorized as forward error correcting (FEC) codes and error detection codes. ECC improves the reliability of NoC with a penalty of overhead power, delay, and area. In this paper, an attempt has been made to reduce the overhead power, delay and area of FEC codes: hamming code and dual rail code, and error detecting codes: checksum and two-dimensional parity with duplication. These ECC are designed in 65 nm technology using CMOS and pass transistor logic and their power–reliability trade-off is analyzed and compared in terms of delay and overhead area. From the results, it is observed that error controlling schemes are providing the best performance with pass transistor logic over error controlling schemes with CMOS logic.

Similar content being viewed by others

References

L. Benini, G. Demicheli, Networks on chips: a new SoC paradigm. Computer 35(1), 70–78 (2002)

L. Benini, G. Demicheli, Networks on Chips: Technology and Tools (Morgan Kaufmann, SanFrancisco, 2006)

D. Bertozzi, L. Benini, G.G. Demicheli, Error control schemes for on chip communication links: the energy-reliability tradeoff. IEEE Trans. Comput. Aidded Des. Integr. Circuits Syst. 24(6), 818–831 (2005)

K.C. Chang, Reliable network on chip design for multi-core system-onchip. J. Supercomput. 55(1), 86–102 (2011)

C. Constantinescu, Trends and challenges in VLSI circuit reliability. IEEE Micro 23(4), 14–19 (2003)

W.J. Dally, B. Towles, Route packets, not wires: on chip interconnection networks. In Proceedings of the Design Automation Conference (LasVegas, 2001), pp. 684–689

W.N. Flayyih, K. Samsudin, Crosstalk-aware multiple error detection scheme based on two dimensional parities for energy efficient network on chip. IEEE Trans. Circuits Syst. 1 61, 2034–2047 (2014)

B. Fu, P. Anpadu, On hamming product codes with type-II hybrid ARQ for on chip interconnects. IEEE Trans. Circuits Syst. I Regul. Pap. 56(9), 2042–2054 (2009)

A. Ganguly, P.P. Pande, B. Belzer, Crosstalk—aware channel coding schemes for energy efficient and reliable NoC interconnects. IEEE Trans. VLSI Syst. 17(11), 1626–1639 (2009)

N. Jafarzadesh, M. Palesi, Data encoding techniques for reducing energy consumption in network-on-chip. IEEE Trans. VLSI Syst. 22(3), 675–685 (2014)

B.K. Kaushik, D. Agarwal, Bus encoder design for reduced crosstalk, power and area in coupled VLSI interconnects. Elsevier Trans. Microelectron. J. 44, 827–833 (2013)

S.E. Lee et al., Low power resilient interconnection with orthogonal latin squares. IEEE Des. Test Comput. 28(2), 30–398 (2011)

S. Mukherjee, Architecture Design for Soft Errors (Morgan Kaufmann, San Francisco, 2008)

S. Murali et al., Analysis of error recovery schemes for networks on chips. IEEE Des. Test Comput. 22(5), 434–442 (2005)

M. Mutyam et al., Fibonacci codes for cross talk avoidance. IEEE Trans. (VLSI) Syst. 20(10), 1899–1903 (2012)

P.P. Pande et al., Energy reduction through crosstalk avoidance coding in network on chip. J. Syst. Archit. 54(3–4), 441–451 (2008)

K.N. Patel, I.L. Markov, Error -correction and cross talk avoidance in DSM buses. IEEE Trans. VLSI Syst. 12(10), 1076–1080 (2004)

Z. Qingli, W. Jinxiang, Y. Yizheng, Low power crosstalk avoidance encoding for on chip data buses, in Proceedings of the IEEE Asia Pacific Conference Circuits Systems (APCCAS2006, 2006), pp. 1611–1614

D. Rossi, A.K. Nieuwland, Power consumption of fault tolerant buses. IEEE Trans. VLSI Syst. 16, 542–553 (2008)

S.R. Sridhara, N.R. Shanbhag, Coding for system on chip networks: a unified frame work. IEEE Trans. VLSI Syst. 13(6), 655–667 (2005)

S.R. Sridhara, N.R. Shanbhag, Coding for reliable on chip buses: a class of fundamental bounds and practical codes. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 26(5), 977–982 (2007)

A. Vitkovski et al., Low power and error protection coding for network on chip traffic. IET Comput. Digit. Tech. 2(6), 483–492 (2008)

Q. Yu, P. Anapadu, Adaptive error controlling for nano meter scale NoC links. IET Comput. Digit. Tech. 3(6), 643–659 (2009). (Special issue on advances in nano electronics circuits and systems)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Chennakesavulu, M., Jayachandra Prasad, T. & Sumalatha, V. Improved Performance of Error Controlling Codes Using Pass Transistor Logic. Circuits Syst Signal Process 37, 1145–1161 (2018). https://doi.org/10.1007/s00034-017-0596-4

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-017-0596-4