Abstract

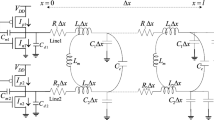

This paper presents an accurate numerical model to evaluate the propagation delay and crosstalk noise of high-speed on-chip interconnects. The structure of on-chip interconnect is considered as non-uniform, including the skin effects. The lossy coupled non-uniform interconnects are modelled by finite-difference time-domain technique. For accurate performance analysis, nonlinear complementary metal–oxide–semiconductor is used to drive the interconnect lines. The nonlinear effects are also incorporated in the proposed model using the improved alpha power law model. The propagation delay and peak noise voltage on the victim line in dynamic and functional switching conditions are analysed and validated with Hailey simulation program with integrated circuit (HSPICE) simulations. The proposed model accuracy and computational efficiency are compared with HSPICE simulations for different cases. The comparison results show that the average error is less than 0.6% while estimating the peak noise voltage using HSPICE. Moreover, the proposed model shows a 75.2% reduction in average CPU runtime compared with HSPICE simulations. Therefore, the proposed model is fast and accurate in predicting the crosstalk-induced performance analysis of lossy coupled non-uniform interconnects at high frequencies.

Similar content being viewed by others

References

R. Achar, S. Nakhla, Simulation of high-speed interconnects. Proc. IEEE 89(5), 693–728 (2001)

K. Agarwal, D. Sylvester, D. Blaauw, Modeling and analysis of crosstalk noise in coupled RLC interconnects. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 25(5), 892–901 (2006)

A. Chatzigeorgiou, S. Nikolaidis, I. Tsoukalas, Modeling CMOS gates driving RC interconnect loads. IEEE Trans. Circuits Syst. II Analog Digit. Signal Process. 48(4), 413–418 (2001)

A.K. Goel, High Speed VLSI Interconnections, 2nd edn. (Wiley, Hoboken, 2007)

S.H. Hall, G.W. Hall, J.A. McCall, High-Speed Digital System Design—A Handbook of Interconnect Theory and Design Practices (Wiley, Hoboken, 2000), pp. 70–93

M. Hayati, A. Lotfi, Compact low pass filter with high and wide rejection in stop band using front coupled tapered CMRC. Electron. Lett. 46(12), 846–848 (2010)

Y.T. Huang, B.C. Dian, W.J. Chappell, Spectral signature decay analysis and new tapered coaxial transmission line spectrometer design. IEEE Trans. Microw. Theory Tech. 61(12), 4630–4635 (2013)

M. Kavicharan, N.S. Murthy, N. Bheema Rao, A. Prathima, Modeling and analysis of on-chip single and H-tree distributed RLC interconnects. Circuits Syst. Signal Process. 35(9), 3049–3065 (2016)

V.R. Kumar, B.K. Kaushik, A. Patnaik, An accurate FDTD model for crosstalk analysis of CMOS-gate-driven coupled RLC interconnects. IEEE Trans. Electromagn. Compat. 56(5), 1185–1193 (2014)

V.R. Kumar, B.K. Kaushik, A. Patnaik, An accurate model for dynamic crosstalk analysis of CMOS gate driven on-chip interconnects using FDTD method. Microelectron. J. 45(4), 441–448 (2014)

V.R. Kumar, B.K. Kaushik, A. Patnaik, Dynamic crosstalk analysis of CMOS driven RLC interconnects using FDTD method, in USNC-URSI Radio Science Meeting (Joint with AP-S Symposium), Lake Buena Vista, FL, USA, vol. 80 (2013)

V.R. Kumar, B.K. Kaushik, A. Patnaik, An unconditionally stable FDTD model for crosstalk analysis of VLSI interconnects. IEEE Trans. Compon. Packag. Manuf. Technol. 5(12), 1810–1817 (2015)

X. Li, J. Mao, M. Swaminathan, Transient analysis of CMOS-gate driven RLGC interconnects based on FDTD. IEEE Trans. CAD Integr. Circuits Syst. 30(4), 574–583 (2011)

S. Mittal, B.K. Kaushik, K.L. Yadav, D.K. Sharma, M.K. Majumder, Crosstalk effect in coupled interconnect lines using FDTD method, in International Conference on Communications, Devices and Intelligent Systems (CODIS), Kolkata, India, pp. 365–368 (2012)

N. Nahman, D. Holt, Transient analysis of coaxial cables using the skin effect approximation A + Bsqrt{s}. IEEE Trans. Circuit Theory 19(5), 443–451 (1972)

C.R. Paul, Incorporation of terminal constraints in the FDTD analysis of transmission lines. IEEE Trans. Electromagn. Compat. 36(2), 85–91 (1994)

J. Rabaey, A. Chandrakasan, B. Nikolic, Digital Integrated Circuits: A Design Perspective, 2nd edn. (Prentice-Hall, Englewood Cliffs, 2003)

J.A. Roden, C.R. Paul, W.T. Smith, D. Gednery, Finite-difference, time-domain analysis of lossy transmission lines. IEEE Trans. Electromag. Compat. 38(1), 15–24 (1996)

T. Sakurai, A.R. Newton, Alpha-power law MOSFET model and its applications to CMOS inverter delay and other formulas. IEEE J. Solid State Circuits 25(2), 584–594 (1990)

V. Sulochana, B. Singh, S. Agrawal, Source code of the proposed model. https://db.tt/AJw6LpZnk7. Accessed 19 Apr 2018

K.T. Tang, E.G. Friedman, Transient analysis of a CMOS inverter driving resistive interconnect, in 2000 IEEE International Symposium on Circuits and Systems. Emerging Technologies for the 21st Century. Proceedings, vol. 4, pp. 269–272 (2000)

K. Watanabe, T. Sekine, Y. Takahashi, A FDTD method for nonuniform transmission line analysis using Yee’s-lattice and wavelet expansion, in IEEE MTT-S International Microwave Workshop Series on Signal Integrity and High-Speed Interconnects, Guadalajara, pp. 83–86 (2009)

J.G. Yook, N.I. Dib, L.P.B. Ratehi, Characterization of high frequency interconnects using finite difference time domain and finite element methods. IEEE Trans. Microw. Theory Tech. 42(9), 1727–1736 (1994)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Sulochana, V., Agrawal, S. & Singh, B. Performance Analysis of Lossy Coupled Non-uniform On-Chip Interconnects with Skin Effects. Circuits Syst Signal Process 38, 1413–1431 (2019). https://doi.org/10.1007/s00034-018-0923-4

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-018-0923-4