Abstract

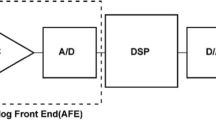

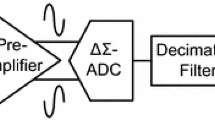

For low-power hearing aid device application, a fully integrated optimized hearing aid SoC structure is proposed in this paper. The SoC consists of high-resolution, low-power analog front-end (AFE), time-division-multiplexed power-on-reset circuit, charge pump, digital signal processing (DSP) platform, and Class-D amplifier. A novel peak-statistical algorithm is proposed to track signal amplitude and adjust automatic gain control loop gain precisely. A comparative DWA is applied to break the correlation of in-band tone and sequential selection scheme, which realizes second-order noise shaping and suppresses harmonic effectively. The SoC has been implemented with 0.13 µm CMOS process. By measurement, it shows that the peak signal-to-noise ratio (SNR) of AFE is 82.6 dB and peak SNR of Class-D amplifier is 79.8 dB. Also, three main algorithms of wide dynamic range compression, noise reduction, and feedback cancelation are executed through DSP platform. With 1 V supply voltage, total SoC power is 1.1 mW and core area is 9.3 mm2. Based on our SoC, a hearing aid device prototype is produced that shows its great potential for mass manufacture in the future.

Similar content being viewed by others

References

R.T. Baird, T.S. Fiez, Linearity enhancement of multibit A/D and D/A converters using data weighted averaging. IEEE Trans. Circuits Syst. II 42, 753–762 (1995)

B.P. Brandt, B.A. Wooley, The 50-MHz multi Sigma–Delta modulator for 12-b 2-MHz A/D converter. IEEE J. Solid-State Circuits 26, 1746–1756 (1991)

K.C. Chang, Y.W. Chen, Y.T. Kuo, C.W. Liu, A low-power hearing aid computing platform using light weight processing elements, in Proceedings of the IEEE International Symposium on Circuits and Systems (2012), pp. 2785–2788

L.M. Chen, Z.H. Yu, C.Y. Chen et al., A 1-V, 1.2-mA fully integrated SoC for digital hearing aids. Microelectronics 46, 12–19 (2015)

I. Deligoz, S. Naqvi, T. Copani et al., A MEMS-based power-scalable hearing aid analog front end. IEEE Trans. Biomed. Circuit Syst. 5(3), 201–214 (2011)

Y. Ephraim, D. Malah, Speech enhancement using a minimum mean-square error short-time spectral amplitude estimator. IEEE Trans. Acoust. Speech Signal Process. 32(6), 109–121 (1984)

D.G. Gata, W. Sjursen, J.R. Hochschild et al., A 1.1-V 270-μA mixed-signal hearing aid chip. IEEE J. Solid-State Circuits 37(12), 1670–1677 (2002)

Y. Geerts, M. Steyaert, Flash A/D specifications of multibit A/D converters, in IEE ADDA, Glasgow, U.K. (1999), pp. 50–53

R. Jacob, CMOS circcuit design, layout, and simulation, 2nd edn. (IEEE John Wiley & Sons press, New York, 2008)

J.M. Kates, Digital hearing aids (Plural Publishing, Oxfordshire, 2008)

P. Khumsat, A. Worapishet, A 0.5 V R-MOSFET-C filter design using subthreshold R-MOSFET resistor and OTAs with cross-forward common-mode cancellation technique. IEEE J. Solid-State Circuits 47(11), 2751–2762 (2012)

S. Kim, S.J. Lee, N. Cho, S. Song, H. Yoo, A fully integrated digital hearing aid chip with human factors considerations. IEEE J. Solid-State Circuits 43(1), 266–274 (2008)

S. Kim, J.Y. Lee, S.J. Song, An energy-efficient analog front-end circuit for a sub-1 V digital hearing aid. IEEE J. Solid-State Circuit 41(4), 876–882 (2006)

K.L. Lee, R.G. Meyer, Low-distortion switched-capacitor filter design techniques. IEEE J. Solid-State Circuits 20, 1103–1113 (1985)

S.H. Lewis, P.R. Gray, A pipelined 5-M sample/s 9-bit analog-to-digital converter. IEEE J. Solid-State Circuits 22(6), 954–961 (1987)

D. Li, Y.T. Yang, Z.C. Shi et al., A low-distortion multi-bit sigma–delta ADC with mismatch-shaping DACs for WLAN applications. Microelectron. J. 46(1), 52–58 (2015)

P. Maleovati, F. Maloberti, M. Terzani, An high-swing, 1.8 V, push-pull op-amp for sigma–delta modulator, in IEEE International Conference on Electronics, Circuits and Systems, vol 1 (1998), pp. 33–36

O. Nys, R. Henderson, An analysis of dynamic element matching techniques in Sigma–Delta modulation, in Proceeding of IEEE International Symposium Circuits and Systems (1996), pp. 231–234

P. Qiao, H. Corporaal, M. Lindwer, A 0.964 mW digital hearing aid system, in Automation and Test in Europe Conference and Exhibition (2011), pp. 1–4

J. Ramirez-Angulo, A.J. Lopez-Martin, R.G. Carvajal et al., Simple class-AB voltage follower with slew rate and bandwidth enhancement and no extra static power or supply requirements. Electron. Lett. 42(14), 784–785 (2006)

C. Ris, S. Dupont, Assessing local noise level estimation methods: application to noise robust ASR. Speech Commun. 34(1), 141–158 (2001)

F. Serra-Graells, L. Gomez, J.L. Huertas, A true 1-V 300-μW CMOS subthreshold log-domain hearing aid on chip”. IEEE J. Solid-State Circuits 39(8), 1271–1281 (2004)

A. Sukumaran, K. Karanjkar, S. Jhanwar, A 1.2 V 285 μA analog front end chip for a digital hearing aid in 0.13 μm CMOS, in Solid-State Circuits Conference (A-SSCC), IEEE Asian, (2013), pp. 397–400

M. Vadipour, Techniques for preventing tonal behavior of data weighted averaging algorithm in Sigma–Delta modulators. IEEE Trans. Circuits Syst. II 47(11), 1137–1144 (2000)

World Health Organization, http://www.who.int/deafness/en/. Accessed 3 Mar 2018

Acknowledgements

This work is supported by the National Natural Science Foundation of China (No. 61704143), Natural Science Foundation of Fujian province (No. 2018J01566), Young- and Middle-aged Teacher Education Research Project of Fujian Province (No. JAT170428), and High-Level Talent Project of Xiamen University of Technology (No. YKJ17019R).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Chen, C., Chen, L. A 79-dB SNR 1.1-mW Fully Integrated Hearing Aid SoC. Circuits Syst Signal Process 38, 2893–2909 (2019). https://doi.org/10.1007/s00034-018-1002-6

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-018-1002-6