Abstract

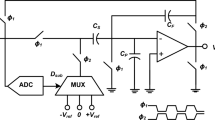

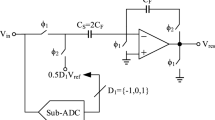

In this paper, a digital background calibration technique for pipelined analog-to-digital converter (ADC) based on the concept of split architecture is proposed to address finite dc gain and nonlinearity of the residue amplifier. In the proposed method, the pipelined ADC divided into two channels where each channel included the first stage followed by an ideal backend ADC. A 1.5 bit per stage is chosen for the first stage of each channel where a pseudorandom sequence is injected before one of the channels. The difference between the digital outputs of two channels is used to drive an interpolation filter to correct the mentioned errors. Since splines modeled high nonlinearity with weakly nonlinear functions, it selected for interpolation filtering which results in low computational overhead and fast convergence time. Behavioral simulations of a 12-bit 100 MS/s pipelined ADC show that the convergence time of the algorithm is approximately 4 × 104 clock cycles and the signal-to-noise and distortion ratio and the spurious free dynamic range improved from 32 dB/35 dB to 70 dB/75 dB.

Similar content being viewed by others

References

H. Adel, M.M. Louerat, M. Sabut, Fast split background calibration for pipelined ADCs enabled by slope mismatch averaging technique. Electron. Lett. 48, 318–320 (2012). https://doi.org/10.1049/el.2012.0357

I. Ahmed, D.A. Johns, An 11-bit 45 MS/s pipelined ADC with rapid calibration of DAC errors in a multibit pipeline stage. IEEE J. Solid-State Circuits 43, 1626–1637 (2008). https://doi.org/10.1109/JSSC.2008.923724

C. DeBoor, A Practical Guide to Splines (Springer, New York, 1978). https://doi.org/10.2307/2006241

P. Gholami, M. Yavari, Digital background calibration with histogram of decision points in pipelined ADCs. IEEE Trans. Circuits Syst. II Exp. Briefs 65, 16–20 (2017). https://doi.org/10.1109/TCSII.2017.2660765

J.K.R. Kim, B. Murmann, A 12-b, 30-MS/s, 2.95-mW pipelined ADC using single-stage class-AB amplifiers and deterministic background calibration. IEEE J. Solid-State Circuits 47, 2141–2151 (2012). https://doi.org/10.1109/JSSC.2012.2194191

G.S. Liu, C.H. Wei, A new variable fractional sample delay filter with nonlinear interpolation. IEEE Trans. Circuits Syst. II Analog Digit. Signal Process. 39, 123–126 (1992). https://doi.org/10.1109/82.205818

H. Mafi, M. Yargholi, M. Yavari, Statistics-based digital background calibration of residue amplifier nonlinearity in pipelined ADCs. IEEE Trans. Circuits Syst. I Regul. Pap. 65, 1–13 (2018). https://doi.org/10.1109/TCSI.2018.2846647

M.A. Montazerolghaem, T. Moosazadeh, M. Yavari, A pre-determined LMS digital background calibration technique for pipelined ADCs. IEEE Trans. Circuits Syst. II Exp. Briefs 62, 841–845 (2015). https://doi.org/10.1109/TCSII.2015.2435071

M.A. Montazerolghaem, T. Moosazadeh, M. Yavari, A single channel split ADC structure for digital background calibration in pipelined ADCs. IEEE Trans. Very Large Scale Integr. Syst. 25, 1563–1567 (2016). https://doi.org/10.1109/TVLSI.2016.2641259

U.K. Moon, B.S. Song, Background digital calibration techniques for pipelined ADCs. IEEE Trans. Circuits Syst. II Analog Digit. Signal Process. 44, 102–109 (1997). https://doi.org/10.1109/82.554434

A. Panigada, I. Galton, Digital background correction of harmonic distortion in pipelined ADCs. IEEE Trans. Circuits Syst. I Regul. Pap. 53, 1885–1895 (2006). https://doi.org/10.1109/TCSI.2006.880034

B. Peng, H. Li, S.C. Lee, P. Lin, Y. Chiu, A virtual-ADC digital background calibration technique for multistage A/D conversion. IEEE Trans. Circuits Syst. II Exp. Briefs 57, 853–857 (2010). https://doi.org/10.1109/TCSII.2010.2082850

B.D. Sahoo, B. Razavi, A 10-b 1-GHz 33-mW CMOS ADC. IEEE J. Solid-State Circuits 48, 1442–1452 (2013). https://doi.org/10.1109/JSSC.2013.2252518

B.D. Sahoo, B. Razavi, A 12-bit 200-MHz CMOS ADC. IEEE J. Solid-State Circuits 44, 2366–2380 (2009). https://doi.org/10.1109/JSSC.2009.2024809

D.L. Shen, T.C. Lee, A linear-approximation technique for digitally-calibrated pipelined A/D converters. in IEEE International Symposium on Circuits and Systems (IEEE, 2005), pp. 1382–1385. https://doi.org/10.1109/ISCAS.2005.1464854

W. Shen, An Introduction to Numerical Computation (World Scientific, New Jersey, 2015). https://doi.org/10.1142/9844

Y.S. Shu, B.S. Song, A 15-bit linear 20-MS/s pipelined ADC digitally calibrated with signal-dependent dithering. IEEE J. Solid-State Circuits 43, 342–350 (2007). https://doi.org/10.1109/JSSC.2007.914260

E. Siragusa, I. Galton, Gain error correction technique for pipelined analogue-to-digital converters. Electron. Lett. 36, 1 (2000). https://doi.org/10.1049/el:20000501

J. Sun, J. Wu, Digital background calibration of pipeline ADC based on correlation. Int. J. Electron. 105, 528–539 (2017). https://doi.org/10.1080/00207217.2017.1378379

B. Zeinali, T. Moosazadeh, M. Yavari, A. Rodriguez-Vazquez, Equalization-based digital background calibration technique for pipelined ADCs. IEEE Trans. Very Large Scale Integr. Syst. 22, 322–333 (2013). https://doi.org/10.1109/TVLSI.2013.2242208

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Zia, E., Farshidi, E. & Kosarian, A. A Split-Based Digital Background Calibration of Pipelined Analog-to-Digital Converters by Cubic Spline Interpolation Filtering. Circuits Syst Signal Process 38, 4799–4816 (2019). https://doi.org/10.1007/s00034-019-01090-5

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-019-01090-5