Abstract

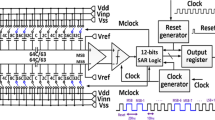

A 10-bit 120 kS/s successive-approximation-register analog-to-digital converter (SAR ADC) is realized for implantable multichannel neural recording system. In order to reduce power consumption and area occupation, an improved energy-efficient VCM-based switching scheme is proposed. Different from the monotonic switching scheme, the switching procedure for each bit cycle of this proposed scheme is almost symmetrical, which facilitates the comparator design. Additionally, since all these capacitors are connected to VCM in the sampling phase, the reset energy of this switching scheme is zero. Bootstrapped sampling switches are employed for linearity improvement. Realized in 0.18-µm CMOS, the proposed ADC occupies an active area of 0.13 mm2. Including the I/O and two 4-to-1 multiplexers, the power consumption is 2.97 µW at 120 kS/s sampling rate. The figure-of-merit of this proposed SAR ADC is about 36.9 fJ/conversion-step.

Similar content being viewed by others

References

C.C. Liu, S.J. Chang, G.Y. Huang, Y.Z. Lin, A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE J. Solid-State Circuits 45(4), 731–740 (2010)

J. Liu, R. Ding, S. Liu, Z. Zhu, A highly energy-efficient, highly area-efficient capacitance multiplexing switching scheme for SAR ADC. Analog Integr. Circuits Signal Process. 96(1), 207–215 (2018)

S.K. Lee, S.J. Park, Y. Suh, H.J. Park, J.Y. Sim, A 1.3 μW 0.6 V 8.7-ENOB successive approximation ADC in a 0.18 μm CMOS, in IEEE Symposium on VLSI Circuits Digest of Technical Papers (2009), pp 242–243

S. Liu, Y. Shen, Z. Zhu, A 12-bit 10MS/s SAR ADC with high linearity and energy-efficient switching. IEEE Trans. Circuits Syst. I Regul. Pap. 63(10), 1616–2016 (2016)

F. Mei, Y. Shu, Y. Yu, A 10-bit 150MS/s SAR ADC with a novel capacitor switching scheme, in IEEE International Conference on Computational Intelligence and Communication Technology (CICT) (2017), pp 1–6

R. Ma, L. Wang, D. Li, R. Ding, Z. Zhu, A 10-bit 100-MS/s 5.23-mW SAR ADC in 0.18-μm CMOS. Microelectron. J. 78, 63–72 (2018)

E. Rahimi, M. Yavari, Energy-efficient high-accuracy switching method for SAR ADCs. Electron. Lett. 50(7), 499–501 (2014)

Y. Shen, Z. Zhu, S. Liu, Y. Yang, A reconfigurable 10-to-12-b 80-to-20-MS/s bandwidth scalable SAR ADC. IEEE Trans. Circuits Syst. I Regul. Pap. 65(1), 51–60 (2018)

X. Tong, M. Ghovanloo, Multichannel wireless neural recording AFE architectures: analysis, modeling, and tradeoffs. IEEE Des. Test 33(4), 24–36 (2016)

X. Tong, M. Ghovanloo, An energy-efficient switching scheme in SAR ADC for biomedical electronics. Electron. Lett. 51(9), 676–678 (2015)

J. Wang, S. Liu, Y. Shen, Z. Zhu, Low-power single-ended SAR ADC using symmetrical DAC switching for image sensors with passive CDS and PGA technique. IEEE Trans. Circuits Syst. I Regul. Pap. 65(8), 2378–2388 (2018)

C. Yuan, Y. Lam, Low-energy and area-efficient tri-level switching scheme for SAR ADC. Electron. Lett. 48(9), 482–483 (2012)

T. Yousefi, A. Dabbaghian, M. Yavari, An energy-efficient DAC switching method for SAR ADCs. IEEE Trans. Circuits Syst. II Exp. Briefs 65(1), 41–45 (2018)

X. Yue, Determining the reliable minimum unit capacitance for the DAC capacitor array of SAR ADCs. Microelectron. J. 44(6), 473–478 (2013)

D. Zhang, A. Bhide, A. Alvandpour, A 53-nW 9.1-ENOB 1-kS/s SAR ADC in 0.13-μm CMOS for medical implant devices. IEEE J. Solid-State Circuits 47(7), 1585–1593 (2012)

H. Zhang, H. Zhang, Q. Sun, J. Li, X. Liu, R. Zhang, A 0.6 V 10-bit 200-kS/s SAR ADC with higher side-reset-and-set switching scheme and hybrid CAP-MOS DAC. IEEE Trans. Circuits Syst. I Regul. Pap. 65(11), 3639–3650 (2018)

W.P. Zhang, X. Tong, Noise modeling and analysis of SAR ADCs. IEEE Trans. VLSI Syst. 23(12), 2922–2930 (2015)

Y. Zhu, C.H. Chan, U.F. Chio, S.W. Sin, U. Seng-Pan, R.P. Martins, F. Maloberti, A 10-bit 100-MS/s reference-free SAR ADC in 90 nm CMOS. IEEE J. Solid-State Circuits 45(6), 1111–1121 (2010)

Z. Zhu, Y. Liang, A 0.6-V 38-nW 9.4-ENOB 20-kS/s SAR ADC in 0.18-μm CMOS for medical implant devices. IEEE Trans. Circuits Syst. I Regul. Pap. 62(9), 2167–2176 (2015)

Acknowledgements

This work was supported by the National Natural Science Foundation of China (Nos. 61674122, 61804124), the key Research and Development Projects in Shaanxi of China (No. 2017KJXX-46) and the Special Support Program for High-level Talents in Shaanxi of China.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Tong, X., Song, M., Chen, Y. et al. A 10-Bit 120 kS/s SAR ADC Without Reset Energy for Biomedical Electronics. Circuits Syst Signal Process 38, 5411–5425 (2019). https://doi.org/10.1007/s00034-019-01138-6

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-019-01138-6