Abstract

In this communication, two novel architectures of voltage mode analog divider circuit and square-root circuit using an operational transconductance amplifier (OTA) have been presented. The proposed divider circuit employs an OTA and two MOSFETs, while the square-root circuit requires one OTA along with one MOSFET. The proposed divider circuit can also be configured as inverse voltage function generator. The performance of the proposed circuits has been validated through Cadence Virtuoso simulations using 0.18 µm CMOS technology parameters. The total power consumption for analog divider circuit is 821 µW, while for square-root circuit, it is 442 µW with ± 0.9 V power supply. Experimental results have also been provided to validate the theory.

Similar content being viewed by others

References

P.E. Allen, D.R. Holberg, CMOS Analog Circuit Design (Oxford University Press, New York, 1987)

M.T. Abuelma’atti, M.L. Al-Qahtani, A current-mode current-controlled current conveyor-based analogue multiplier/divider. Int. J. Electron. 85(1), 71–77 (1998)

M.A. Al-Absi, A. Hussein, M.T. Abulma’atti, A low voltage and low power current-mode analog computational circuit. Circuits, Syst., Sig. Process. 32(1), 321–331 (2013)

E.S. Al-Suhaibani, M.A. Al-Absi, A new CMOS current-mode controllable-gain square rooting circuit using MOSFET in subthreshold. Analog Integr. Circuits Sig. Process 82(2), 431–434 (2015)

G. Aggarwal, H. Garg, N. Bansal, P. Gangwar, R. Pandey, Single OTRA based Low voltage square root circuit. Int. J. Adv. Res. Innov. 5(4), 431–432 (2017)

M. Bhanja, B.N. Ray, OTA-based logarithmic circuit for arbitrary input signal and its application. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 24(2), 638–649 (2016)

N. Bajaj, J. Govil, Realisation of a differential multiplier-divider based on current feedback amplifiers, in International Conference on Semiconductor Electronics (IEEE, 2006), pp. 708–712

W. Chiu, S.-I. Liu, H.-W. Tsao, J.-J. Chen, CMOS differential difference current conveyors and their applications. IEE Proc. Circuits Dev. Syst. 143(2), 91–96 (1996)

E.O. Doebelin, Measurement Systems: Application and Design (McGraw Hill, New York, 2004)

K. Dejhan, C. Netbut, New simple square-rooting circuits based on translinear current conveyors. Int. J. Electron. 94(7), 707–723 (2007)

I.M. Filanovsky, H.P. Baltes, Simple CMOS analog square-rooting and squaring circuits. IEEE Trans. Circuits Syst. 39(4), 312–315 (1992)

D. Ghosh, D. Patranabis, A simple analog divider having independent control of sensitivity and design conditions. IEEE Trans. Instrum. Meas. 39(3), 522–526 (1990)

E.W. Greeneich, Analog Integrated Circuits (International Thomson Publishing, Stamford, 1997)

Y.S. Hwang, W.H. Liu, S.H. Tu, J.J. Chen, New building block: multiplication-mode current conveyor. IET Circuits Dev. Syst. 3(1), 41–48 (2009)

W. Jaikla, M. Siripruchyanun, A novel current-mode multiplier/divider employing only single dual-output current controlled CDTA, in 2007 International Symposium on Communications and Information Technologies (IEEE, 2007), pp. 106–109

K. Kaewdang, C. Fongsamut, W. Surakampontorn, A wide band current-mode OTA based analog multiplier-divider, in Proceedings of the 2003 International Symposium on Circuits and Systems (2003), pp. 349–352

M. Kumngern, U. Torteanchai, A CMOS current-mode multiplier/divider using a current amplifier, in 7th International Power Engineering and Optimization Conference (PEOCO) (IEEE, 2013), pp. 742–745

M. Kumngern, U. Torteanchai, OTA-based current square rooting circuit. Far East J. Electron. Commun. 17(1), 127–140 (2017). https://doi.org/10.17654/ec017010127

A.J. Lopez-Martin, A. Carlos, J. Ramirez-Angulo, R.G. Carvajal, Compact low-voltage CMOS current-mode multiplier/divider, in International Symposium on Circuits and Systems (IEEE, 2010), pp. 1583–1586

W. Liu, S.-I. Liu, S.K. Wei, CMOS current-mode divider and its applications. IEEE Trans. Circuits Syst.-II: Express Briefs 52(3), 145–148 (2005)

S.-I. Liu, J.J. Chen, Realisation of analogue divider using current feedback amplifiers. IEE Proc. Circuits, Dev. Syst. 142(1), 45–48 (1995)

S.-I. Liu, D.S. Wu, H.W. Tsao, J. Wu, J.H. Tsay, Nonlinear circuit applications with current conveyors. IEE Proc. G-Circuits, Dev. Syst. 140(1), 1–6 (1993)

S.-I. Liu, Square-rooting and vector summation circuits using current conveyors. IEE Proc. Circuit, Dev. Syst. 142(4), 223–226 (1995)

P. Mongkolwai, W. Tangsrirat, CFTA-based current multiplier/divider circuit, in 2011 International Symposium on Intelligent Signal Processing and Communications Systems (ISPACS) (IEEE, 2011), pp. 1–4

W. Narksarp, P. Pawarangkoon, W. Kiranon, P. Wadkien, A four-quadrant current-mode multiplier/divider building block, in 2009 6th International Conference on Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology (IEEE, 2009), pp. 574–577

B.C. Nagar, S.K. Paul, Single OTRA based two quadrant analog voltage divider. Analog Integr. Circuits Sig. Process 94(1), 161–169 (2018)

S. Parsnejad, Y. Hu, H. Wan, E. Ashoori, A.J. Mason, Wide dynamic range multi-channel electrochemical instrument for in-field measurements, in IEEE Sensors (2016), pp. 1–3

W. Petchakit, W. Kiranon, P. Wardkien, S. Petchakit, A current-mode CCCII-based analog multiplier/divider, in ECTI-CON2010: The 2010 ECTI International Confernce on Electrical Engineering/Electronics, Computer, Telecommunications and Information Technology (IEEE, 2010), pp. 221–224

N. Pisutthipong, M. Siripruchyanun, A novel simple current-mode multiplier/divider employing only single multiple-output current controlled CTTA, in TENCON 2009 IEEE Region 10 Conference (IEEE, 2009), pp. 1–4

J.K. Pathak, A.K. Singh, R. Senani, New squaring and square-rooting circuits using CDBA. Am. J. Electr. Electron. Eng. 2(6), 175–179 (2014)

K.D. Peterson, A. Nedungadi, R.L. Geiger, Amplifier design considerations for high frequency monolithic filters, in Proceedings of European Conference on Circuit Theory and Design (ECCTD) (1987), pp. 321–326

V. Riewruja, T. Kamsri, Square-rooting and absolute function circuits using operational amplifiers. IET Circuits Dev. Syst. 3(2), 57–63 (2009)

V. Riewruja, Simple square-rooting circuit using OTAs. Electron. Lett. 44(17), 1000–1002 (2008)

W. Surakampontorn, K. Khanittha, F. Chalermpan, A simple current-mode analog multiplier-divider circuit using OTAs, in Proceedings of the IEEE Conference (2002), pp. 658–661

M. Siripruchyanun, A design of analog multiplier and divider using current controlled current differencing buffered amplifiers, in Proceedings of the International Symposium on Integrated Circuits (ISIC’07) (2007), pp. 568–571

M. Siripruchyanun, W. Jakila, A current-mode multiplier/divider based on CCCDTA. Int. J. Electron. Commun. (AEU) 62(3), 223–227 (2008)

E.S. Sinencio, J.R. Angulo, B.L. Barranco, A.R. Vazquez, Operational transconductance amplifier-based nonlinear function syntheses. IEEE J. Solid-State Circuits 24(6), 1576–1586 (1989)

N. Tadic, D. Gobovic, Smart sensor interfacing circuit using square-rooting current-to-frequency conversion. Int. J. Electron. 94(12), 1075–1098 (2007)

W. Tangsrirat, T. Pukkalanun, P. Mongkolwai, W. Surakampontorn, Simple current-mode analog multiplier, divider, square-rooter and squarer based on CDTAs. Int. J. Electron. Commun. (AEU) 65(3), 198–203 (2011)

K.S. Tarun, R. Arabinda, N.R. Baidyanath, An arbitrary power law device based on operational transconductance amplifiers. IEEE Trans. Instrum. Meas. 42(5), 948–952 (1993)

H. Wasaki, Y. Horio, S. Nakamura, Current multiplier/divider circuit. Electron. Lett. 27(6), 504–506 (1991)

Z. Wang, A CMOS four-quadrant analog multiplier with single-ended voltage output and improved temperature performance. IEEE J. Solid-State Circuits 26(9), 1293–1301 (1991)

Acknowledgements

The authors gratefully acknowledge Professor Raj Senani, Department of Electronics and Communication Engineering, Netaji Subhas University of Technology, New Delhi, India, for his help and valuable suggestions in the preparation of this manuscript. The authors also wish to thank the anonymous reviewers for their constructive comments and suggestions in improving the quality of the manuscript.

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Appendix

Appendix

1.1 Variation in VP Due to Changes in VDD

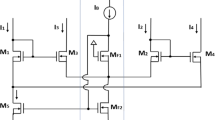

For generation of external voltage VP, we have used a voltage divider circuit with three matched MOSFETs (operating in saturation region) (Fig. 25).

The current flowing through each MOSFET is same and is equal to:

Solving Eqs. (23–25), assuming equal threshold voltages, we get:

Now, in Eq. (26), if a deviation is introduced in VDD by a value of ± ΔVDD, then Eq. (26) becomes:

Therefore, from Eq. (27), the effect of changes in VDD may be made negligible small, if (W/L)2 ≫ (W/L)1 and (W/L)2 ≫ (W/L)3.

Rights and permissions

About this article

Cite this article

Raj, A., Bhaskar, D.R. & Kumar, P. Two Quadrant Analog Voltage Divider and Square-Root Circuits Using OTA and MOSFETs. Circuits Syst Signal Process 39, 6358–6385 (2020). https://doi.org/10.1007/s00034-020-01454-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-020-01454-2