Abstract

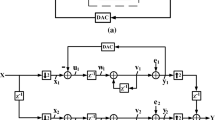

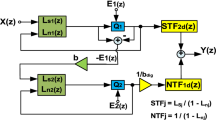

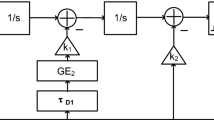

A low-complexity stochastic dynamic element matching (DEM) technique to mitigate the distortions caused by the nonlinearity of multi-bit digital-to-analog converters (DACs) in sigma-delta modulator is proposed. Multi-bit DAC noise is analyzed in detail from a signal processing point-of-view in this research, and then implementation of the basic stochastic unit named swapper cell which includes bar state and cross state controlled by a 1-bit pseudo-random noise signal, is illustrated. To reduce the hardware complexity, a multi-layer scheme for multi-input multi-output stochastic encoder is presented and demonstrated based on rigorous mathematical derivation. For a n-input n-output version, the number of the switch elements employed in the proposed encoder is reduced to 2nlog2n from the conventional n!. Simulation results show that, with the use of the stochastic encoder, severe harmonic distortions resulted by the DAC elements mismatch errors are suppressed effectively. When the proposed encoders are applied to the internal multi-bit DACs in sigma-delta (ΣΔ) modulators, large improvements of the linearity performance of the modulators are achieved. Additionally, the analyses and explanations for this stochastic scheme provide a theoretical foundation for the future development of noise shaping DEM.

Similar content being viewed by others

References

M. Akbari, O. Hashemipour, F. Moradi, Design and analysis of an ultra-low-power second-order asynchronous delta-sigma modulator. Circuits Syst. Signal Process. 36(2), 4919–4936 (2017)

J. Bastos, A.M. Marques, M.S.J. Steyaert, W. Sansen, A 12-bit intrinsic accuracy high-speed CMOS DAC. IEEE J. Solid State Circuit 33(12), 1959–1969 (1998)

K.L. Chan, J. Zhu, I. Galton, A 150MS/s 14-bit segmented DEM DAC with greater than 83 dB of SFDR across the Nyquist band, in IEEE Symposium VLSI Circuit (2007), pp. 200–201

Y. Cong, R.L. Geiger, A 1.5-V 14-bit 100-MS/s self-calibrated DAC. IEEE J. Solid State Circuit 38(12), 2051–2060 (2013)

J.R. Custódio, J. Goes, N. Paulino, J.P. Oliveira, E. Bruun, A 1.2-V 165-µW 0.29-mm2 multibit sigma-delta ADC for hearing aids using nonlinear DACs and with over 91 dB dynamic-range. IEEE Trans. Biomed. Circuits Syst. 7(3), 376–385 (2013)

E. Fogelman, J. Welz, I. Galton, An audio ADC delta-sigma modulator with 100-dB peak SINAD and 102-dB DR using a second-order mismatch-shaping DAC. IEEE J. Solid State Circuits 36(3), 339–348 (2001)

I. Galton, Why dynamic-element-matching DACs work. IEEE Trans. Circuits Syst. II Expr. Briefs 57(2), 69–74 (2010)

A.M. Geert, J. Vandenbussche, W. Sansen, M.S.J. Steyaert, G.G.E. Gielen, A 14-bit intrinsic accuracy Q2 random walk CMOS DAC. IEEE J. Solid State Circuit 34(12), 1708–1718 (1999)

Q. Huang, P.A. Francese, C. Martelli, J. Nielsen, A 200 MS/s 14 b 97 mW DAC in 0.18 μm CMOS, in IEEE International Solid-State Circuits Conference (2004), pp. 364–532

I.-S. Hwang, W.-D. Tseng, I.-F. Huang, Integrated fault tolerant connections-scheduling for dilated Benes network. IET Proc. Commun. 152(3), 343–348 (2005)

B. Jewett, J. Liu, K. Poulton, A 1.2Gs/s 15b DAC for precision signal generation, in IEEE International Digest of Technical Papers. Solid-State Circuits Conference (2005), pp. 110–587

B. Khazaeili, M. Yavari, A simple structure for MASH ΣΔ modulators with highly reduced in-band quantization noise. Circuits Syst. Signal Process. 36(5), 2125–2153 (2017)

T. Kim, C. Han, N. Maghari, A 4th-order continuous-time delta-sigma modulator using 6-bit double noise-shaped quantizer. IEEE J. Solid State Circuits 52(12), 3248–3261 (2017)

D. Kong, I. Galton, Subsampling mismatch noise cancellation for high-speed continuous-time DACs. IEEE Trans. Circuits Syst. 66(8), 2843–2853 (2019)

Y.S. Kwak, K.I. Cho, H.J. Kim, S.H. Lee, G.C. Ahn, A 72.9-dB SNDR 20-MHz BW 2-2 discrete-time resolution-enhanced sturdy mash delta-sigma modulator using source-follower-based integrators. IEEE J. Solid State Circuits 53(10), 2772–2782 (2018)

S.C. Lee, C. Yun, A 15-MHz bandwidth 1-0 MASH ΔΣ ADC with nonlinear memory error calibration achieving 85-dBc SFDR. IEEE J. Solid State Circuits 49(3), 695–707 (2014)

B.-C. Lin, S. Chen, Y. Huang, C.-T. Lea, Power minimization in microring-based benes networks. IEEE Trans. Commun. 66(8), 3517–3525 (2018)

E. Nieminen, On quadratic permutation polynomials, turbo codes, and butterfly networks. IEEE Trans. Inf. Theory 63(9), 5793–5801 (2017)

V. O’Brien, A.G. Scanlan, B. Mullane, A reduced hardware ISI and mismatch shaping DEM decoder. Circuits Syst. Signal Process. 37(6), 2299–2317 (2018)

K. O’Sullivan, C. Gorman, M. Hennessy, V. Callaghan, A 12-bit 320-MSample/s current-steering CMOS D/A converter in 0.44 mm2. IEEE J. Solid State Circuits 39(7), 1064–1072 (2004)

J. Remple, I. Galton, The effects of inter-symbol interference in dynamic element matching DACs. IEEE Trans. Circuits Syst. I Reg. Pap. 64(1), 14–23 (2017)

P. Rombouts, M.D. Bock, J.D. Maeyer, L. Weyten, A describing function study of saturated quantization and its application to the stability analysis of multi-bit sigma delta modulators. IEEE Trans. Circuits Syst. I Reg. Pap. 60(7), 1740–1752 (2013)

E. Roverato, M. Kosunen, K. Cornelissens et al., Power-scalable dynamic element matching for a 3.4-GHz 9-bit ΔΣ RF-DAC in 16-nm FinFET. IEEE Solid State Circuits Lett. 1(5), 126–129 (2018)

A. Sanyal, L. Chen, N. Sun, Dynamic element matching with signal-independent element transition rates for multibit ΔΣ modulators. IEEE Trans. Circuits Syst. I Reg. Pap. 62(5), 1325–1334 (2015)

W. Schofield, D. Mercer, L.S. Onge, A 16b 400MS/s DAC with < -80dBc IMD to 300 MHz and < -160dBm/Hz noise power spectral density, in IEEE International Solid-State Circuits Conference, 2003. Digest of Technical Papers (2003), pp. 126–482

Y. Wang, T. He, P. Silva, Y. Zhang, G.C. Temes, Wide-band high-accuracy ΔΣ ADC using segmented DAC with DWA and mismatch shaping. Electron. Lett. 53(11), 713–714 (2017)

B. Wang, L. Liu, C. Deng, M. Zhu et al., Exploration of benes network in cryptographic processors: a random infection countermeasure for block ciphers against fault attacks. IEEE Trans. Inf. Forensics Secur. 12(2), 309–322 (2017)

B. Wang, S.-W. Sin, S.-P.U.F. Maloberti, R.P. Martins, A 550-μW 20-kHz BW 100.8-dB SNDR linear exponential multi-bit incremental ΣΔ ADC With 256 clock cycles in 65-nm CMOS. IEEE J. Solid State Circuits 54(4), 1161–1172 (2019)

J. Welz, I. Galton, Necessary and sufficient conditions for mismatch shaping in a general class of multibit DACs. IEEE Trans. Circuit Syst. II Analog Dig. Sig. Proc. 49(12), 748–759 (2002)

Y. Zhang, X. He, K.-P. Pun, An extremely linear multi-level DAC for continuous-time delta-sigma modulators. IEEE Trans. Circuits Syst. II Expr. Briefs 66(3), 367–371 (2019)

Acknowledgements

This research is supported by National Natural Science Foundation of China (Grant Nos. 61504102 and 11604251) and the National Key Project of Intergovernmental Cooperation in International Scientific and Technological Innovation (2016YFE0107900).

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Li, D., Fei, C. & Zhang, Q. Analysis and Design of Low-Complexity Stochastic DEM Encoder for Reduced-Distortion Multi-bit DAC in Sigma-Delta Modulators. Circuits Syst Signal Process 40, 296–310 (2021). https://doi.org/10.1007/s00034-020-01470-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-020-01470-2