Abstract

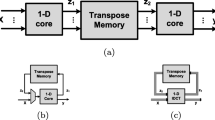

Applications such as multimedia and system on chip require multiple transforms for processing various types of signals such as text, audio, image and video. Hybrid architectures supporting multiple transforms improve the overall performance of the system. In this work, reduced form of discrete Fourier transform (DFT), discrete cosine transform (DCT), discrete sine transform (DST) and opitimized form of discrete Hartley transform (DHT) and Haar Wavelet Transform (HWT) are proposed to design a hybrid architecture that supports multiple discrete transforms of order-8. An architecture is designed by considering the computational needs across transforms with a blend of concurrent and sequential computations through mode control. In existing literature limited work is reported on hybrid architectures for sinusoidal and non-sinusoidal transforms DFT, DCT, DST, DHT and HWT. In this paper authors propose a pipelined and parallel architecture for multiple 8-point transforms which is capable of producing the outputs in two modes, namely, sequential and concurrent. Novelty of the approach is to have a provision to select an appropriate transform for an application and also choose multiple transforms as per requirement. Since, these transforms are used in various applications, the proposed approach is useful in heterogeneous systems requiring output from multiple transforms either in parallel or sequential mode. A prototype of the proposed architecture is implemented using Xilinx ISE tools with the target FPGA as Virtex 6 xc6vlx760ff1760-2. The results are verified using Matlab implementation with mean square error of 2.2497 × 10–9. Compared to the standalone architectures and other similar architectures, the proposed hybrid architecture has shown improvement in area-time complexity with a throughput of at least 4 × due to increased level of parallelism and pipelining.

Similar content being viewed by others

Explore related subjects

Discover the latest articles and news from researchers in related subjects, suggested using machine learning.References

J. Altermann, E. Costa, S. Almeida, High performance Haar Wavelet transform architecture, in 2011 20th European Conference on Circuit Theory and Design (ECCTD), pp. 596–599. IEEE (2011)

A. Amira, An FPGA based parameterizable system for discrete Hartley transforms implementation, in Proceedings 2003 International Conference on Image Processing, vol. 2, pp. II-567. IEEE (2003)

H.C. Andrews, K.L. Caspari, A generalized technique for spectral analysis. IEEE Trans. Comput. 100(1), 16–25 (1970)

F. Arguello, J.D. Bruguera, R. Doallo, E.L. Zapata, Parallel architecture for fast transforms with trigonometric kernel. IEEE Trans. Parallel Distrib. Syst. 5(10), 1091–1099 (1994)

R.E. Atani, S. Mirzakuchaki, F. Samii, M.R. Nasrollahzadeh, Design and implementation of a 157 MHz DA-Based DXT coprocessor, in 4 IEEGCC Conference, Manama, Kingdom of Bahrain, pp. 11–14 (2007)

M. Budagavi, A. Fuldseth, G. Bjøntegaard, V. Sze, M. Sadafale, Core transform design in the high efficiency video coding (HEVC) standard. IEEE J. Sel. Top. Signal Process. 7(6), 1029–1041 (2013)

V. Chandran, I. Mamatha, S. Tripathi, NEDA based hybrid architecture for DCT–HWT, in 2016 IEEE International Conference on VLSI Systems, Architectures, Technology and Applications (VLSI-SATA), pp. 1–6. IEEE (2016)

C.H. Chang, C.L. Wang, Y.T. Chang, Efficient VLSI architectures for fast computation of the discrete Fourier transform and its inverse. IEEE Trans. Signal Process. 48(11), 3206–3216 (2000)

Y.C. Chao, S.T. Wei, C.H. Kao, B.D. Liu, J.F. Yang, An efficient architecture of multiple 8× 8 transforms for H. 264/AVC and VC-1 decoders, in The 2010 International Conference on Green Circuits and Systems, pp. 595–598. IEEE (2010)

Z. Chen, Q. Han, W.K. Cham, Low-complexity order-64 integer cosine transform design and its application in HEVC. IEEE Trans. Circuits Syst. Video Technol. 28(9), 2407–2412 (2018)

D.F. Chiper, A novel VLSI DHT algorithm for a highly modular and parallel architecture. IEEE Trans. Circuits Syst. II Express Briefs 60(5), 282–286 (2013)

J.W. Cooley, J.W. Tukey, An algorithm for the machine computation of complex Fourier series. Math. Comp. 19, 297–301 (1965)

B. Das, S. Banerjee, Unified CORDIC-based chip to realize DFT/DHT/DCT/DST. IEE Proc. Comput. Digital Tech. 149(4), 121–127 (2002)

T. Dias, N. Roma, L. Sousa, Unified transform architecture for AVC, AVS, VC-1 and HEVC high-performance codecs. EURASIP J. Adv. Signal Process. 1, 1–15 (2014)

T. Diasa, N. Romaa, L. Sousaa, Exploiting coarse-grained parallelism in multi-transform architectures for H. 264/AVC high profile codecs. Procedia Technol. 17, 154–161 (2014)

M. Ezhilarasan, P. Thambidurai, A hybrid Transformation Technique for Video Coding. Lecture Notes in Computer Science (Springer, Berlin, 2006), pp. 503–508

M. Garrido, N.K. Unnikrishnan, K.K. Parhi, A serial commutator fast Fourier transform architecture for real-valued signals. IEEE Trans. Circuits Syst. II Express Briefs 65(11), 1693–1697 (2017)

R.C. Gonzalez, R.E. Woods, Digital Image Processing, 4th edn. (Pearson Education Limited, London, 2018)

J.I. Guo, C.C. Li, A generalized architecture for the one-dimensional discrete cosine and sine transforms. IEEE Trans. Circuits Syst. Video Technol. 11(7), 874–881 (2001)

J.I. Guo, C.M. Liu, C.W. Jen, A general approach to design VLSI arrays for the multi-dimensional discrete Hartley transform, in Proceedings of IEEE International Symposium on Circuits and Systems-ISCAS'94, vol. 4, pp. 235–238. IEEE (1994)

H. Ho, V. Szwarc, T. Kwasniewski, A reconfigurable systolic array architecture for multicarrier wireless and multirate applications. Int. J. Reconfig. Comput. 1, 1–14 (2009)

S.F. Hsiao, W.R. Shiue, Design of low-cost and high-throughput linear arrays for DFT computations: algorithms, architectures, and implementations. IEEE Trans. Circuits Syst. II Analog Digital Signal Process. 47(11), 1188–1203 (2000)

S.F. Hsiao, W.R. Shiue, Low-cost unified architectures for the computation of discrete trigonometric transforms, in 2000 IEEE International Conference on Acoustics, Speech, and Signal Processing. Proceedings (Cat. No. 00CH37100), vol. 6, pp. 3299–3302. IEEE (2000)

H. Huang, L. Xiao, J. Liu, CORDIC-based unified architectures for computation of DCT/IDCT/DST/IDST. Circuits Syst. Signal Process. 33(3), 799–814 (2014)

N. Jarray, M. Elhajji, A. Zitouni, Efficient Hybrid DWT-DCT architecture for wireless capsule endoscopy, in 2018 15th International Multi-Conference on Systems, Signals & Devices (SSD), pp. 263–268. IEEE (2018)

M. Jridi, P.K. Meher, Scalable approximate DCT architectures for efficient HEVC-compliant video coding. IEEE Trans. Circuits Syst. Video Technol. 27(8), 1815–1825 (2016)

M.H. Lee, M.H.A. Khan, K.J. Kim, D. Park, A fast hybrid Jacket-Hadamard matrix based diagonal block-wise transform. Signal Process. Image Commun. 29(1), 49–65 (2014)

C.T. Lin, Y.C. Yu, L.D. Van, Cost-effective triple-mode reconfigurable pipeline FFT/IFFT/2-D DCT processor. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 16(8), 1058–1071 (2008)

K.R. Liu, C.T. Chiu, Unified parallel lattice structures for time-recursive discrete cosine/sine/Hartley transforms. IEEE Trans. Signal Process. 41(3), 1357–1377 (1993)

C. Loeffler, A. Ligtenberg, G.S. Moschytz, Practical fast 1-D DCT algorithms with 11 multiplications, in International Conference on Acoustics, Speech, and Signal Processing, pp. 988–991. IEEE (1989)

P.K. Meher, T. Srikanthan, J.C. Patra, Scalable and modular memory-based systolic architectures for discrete Hartley transform. IEEE Trans. Circuits Syst. I Reg. Pap. 53(5), 1065–1077 (2006)

P.K. Meher, Highly concurrent reduced complexity 2-D systolic array for discrete Fourier transform. IEEE Signal Proc. Lett. 13(8), 481–484 (2006)

N.R. Murthy, M.N.S. Swamy, On the real-time computation of DFT and DCT through systolic architectures. IEEE Trans. Signal Process. 42(4), 988–991 (1994)

M. Nair, I. Mamatha, S. Tripathi, Distributed arithmetic-based hybrid architecture for multiple transforms, in Advances in Signal Processing and Communication, pp. 221–232. Springer, Singapore (2019)

A. Nandi, S. Patil, Performance evaluation of one dimensional systolic array for FFT processor, in 2007 International Conference on Signal Processing, Communications and Networking, pp. 168–171. IEEE (2007)

R.S. Oliveira, R.J. Cintra, F.M. Bayer, T.L. da Silveira, A. Madanayake, A. Leite, Low-complexity 8-point DCT approximation based on angle similarity for image and video coding. Multidimension. Syst. Signal Process. 30(3), 1363–1394 (2019)

S.B. Pan, R.H. Park, Unified systolic arrays for computation of the DCT/DST/DHT. IEEE Trans. Circuits Syst. Video Technol. 7(2), 413–419 (1997)

D. Puchala, Approximate calculation of 8-point DCT for various scenarios of practical applications. EURASIP J. Image Video Process. 1, 1–34 (2021)

M. Puschel, J.M. Moura, Algebraic signal processing theory: Cooley-Tukey type algorithms for DCTs and DSTs. IEEE Trans. Signal Process. 56(4), 1502–1521 (2008)

C.H. Rao, M. Latha, A novel VLSI architecture of hybrid image compression model based on reversible blockade transform. World Acad. Sci. Eng. Technol. 52, 1016–1022 (2009)

N.M. Sk, Discrete Orthogonal Multi-transform on Chip (DOMoC). J. Signal Process. Syst. 91(5), 437–457 (2019)

T.Y. Sung, Y.S. Shieh, H.C. Hsin, An efficient VLSI linear array for DCT/IDCT using subband decomposition algorithm. Mathematical Problems in Engineering, pp. 1–21, Hindawi Publishing Corporation (2010)

Y. Voronenko, M. Puschel, Algebraic signal processing theory: Cooley-Tukey type algorithms for real DFTs. IEEE Trans. Signal Process. 57(1), 205–222 (2009)

K. Wahid, S. Shimu, M. Islam, D. Teng, M.H. Lee, S.B. Ko, Efficient hardware implementation of hybrid cosine-Fourier-wavelet transforms on a single FPGA, in 2009 IEEE International Symposium on Circuits and Systems (ISCAS), pp. 2325–2328. IEEE (2009)

K.A. Wahid, M.A. Islam, S.S. Shimu, M.H. Lee, S.B. Ko, Hybrid architecture and VLSI implementation of the Cosine–Fourier–Haar transforms. Circuits Syst. Signal Process. 29(6), 1193–1205 (2010)

Funding

Not applicable.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors have no conflict of interest/competing interests.

Consent for Publication

The authors give consent for publication after article acceptance.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Mamatha, I., Tripathi, S. & Sudarshan, T.S.B. Hybrid Architecture for Sinusoidal and Non-sinusoidal Transforms. Circuits Syst Signal Process 41, 3903–3930 (2022). https://doi.org/10.1007/s00034-022-01963-2

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-022-01963-2