Abstract

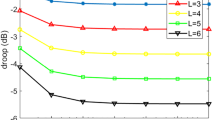

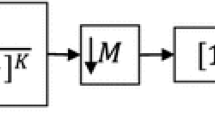

This paper proposes low-cost wide-band generic cascaded-integrator-comb decimation filters with improved magnitude response. The decimation structures are realized as cascade of sharpening sections, where decimation factor M expressed as \(M = M_1M_2\), \(M_1, M_2 \in {\mathbb {Z}}^+\). The proposed decimation structure-I minimizes pass-band droop using a cascade of Kaiser Hamming (KH) and Saramäki–Ritoniemi (SR) sharpening structures. The first stage decimates the signal by \(M_1\) using KH sharpening, followed by SR sharpening in the second stage to down-sample it further by \(M_2\). The coefficients of SR structure are determined using linear programming in MATLAB. The proposed decimation structure-I designed for various integer decimation factors provides an average pass-band droop of \(-\,0.09\) dB at the normalized frequency of 1/2M and an average alias rejection of \(-\,44\) dB at the normalized frequency of 3/2M. The decimation structure-II further increases the alias rejection by using two-passes of SR structure. It achieves an average alias rejection of \(-\,87\) dB, but has slightly inferior pass-band droop of \(-\,0.17\) dB. The proposed designs when implemented on FPGA (field programmable gate arrays) have lower slice requirement and achieve higher maximum operating frequency than other existing competing designs. The performance of proposed decimation filters is confirmed using computer simulations of analog-to-digital converters and sigma-delta modulators.

Similar content being viewed by others

Data availability

There are no associated data with this manuscript. However, any information required can be made available by the corresponding author upon reasonable request. The email-id of the corresponding author is available on first page of the manuscript.

References

S. Aggarwal, Improved two-stage decimator structure using Kaiser Hamming sharpening. Circuits Syst. Signal Process. 40, 2584–2598 (2021)

C. Candan, Optimal sharpening of CIC filters and an efficient implementation through Saramäki–Ritoniemi decimation filter structure (extended version) (2012)

J.O. Coleman, Chebyshev stopbands for CIC decimation filters and CIC-implemented array tapers in 1D and 2D. IEEE Trans. Circuits Syst. I Regul. Pap. 59(12), 2956–2968 (2012)

G.J. Dolecek, L.M. Barba-Maza, Modified corrector-comb-based decimator with improved passband and aliasing rejection, in 2019 IEEE 62nd International Midwest Symposium on Circuits and Systems (MWSCAS), pp. 1159–1162 (2019)

G.J. Dolecek, M. Laddomada, An economical class of droop-compensated generalized comb filters: analysis and design. IEEE Trans. Circuits Syst. II Express Briefs 57(4), 275–279 (2010)

G.J. Dolecek, S.K. Mitra, Two-stage CIC-based decimator with improved characteristics. IET Signal Process. 4(1), 22–29 (2010). https://doi.org/10.1049/iet-spr.2008.0160

A. Dudarin, G. Molnar, M. Vucic, Optimum multiplierless compensators for sharpened cascaded-integrator-comb decimation filters. Electron. Lett. 54(16), 971–972 (2018)

A. Fernandez-Vazquez, G.J. Dolecek, Maximally flat CIC compensation filter: design and multiplierless implementation. IEEE Trans. Circuits Syst. II Express Briefs 59(2), 113–117 (2012)

C. Gan, X. Li, Improved CIC decimation filter on software defined radio, in 2021 9th International Conference on Communications and Broadband Networking, ICCBN 2021 (Association for Computing Machinery, New York, NY, USA, 2021), pp. 232–238. https://doi.org/10.1145/3456415.3456453

E. Hogenauer, An economical class of digital filters for decimation and interpolation. IEEE Trans. Acoust. Speech Signal Process. 29(2), 155–162 (1981)

G. Jovanovic-Dolecek, S.K. Mitra, A new two-stage sharpened comb decimator. IEEE Trans. Circuits Syst. I Regul. Pap. 52(7), 1414–1420 (2005). https://doi.org/10.1109/TCSI.2005.851390

J. Kaiser, R. Hamming, Sharpening the response of a symmetric nonrecursive filter by multiple use of the same filter. IEEE Trans. Acoust. Speech Signal Process. 25(5), 415–422 (1977)

A.Y. Kwentus, Zhongnong Jiang, A.N. Willson, Application of filter sharpening to cascaded integrator-comb decimation filters. IEEE Trans. Signal Process. 45(2), 457–467 (1997). https://doi.org/10.1109/78.554309

G. Molnar, A. Dudarin, M. Vucic, Design and multiplierless realization of maximally flat sharpened-CIC compensators. IEEE Trans. Circuits Syst. II Express Briefs 65(1), 51–55 (2018)

G. Molnar, M.G. Pecotic, M. Vucic, Weighted least-squares design of sharpened CIC filters, in 2013 36th International Convention on Information and Communication Technology, Electronics and Microelectronics (MIPRO), pp. 91–95 (2013)

G. Molnar, M. Vucic, Weighted minimax design of sharpened CIC filters, in 2013 IEEE 20th International Conference on Electronics, Circuits, and Systems (ICECS), pp. 869–872 (2013)

T. Saramäki, T. Ritoniemi, A modified comb filter structure for decimation, vol. 4, pp. 2353–2356 (1997)

G. Stephen, R.W. Stewart, High-speed sharpening of decimating CIC filter. Electron. Lett. 40(21), 1383–1384 (2004)

D.E. Troncoso Romero, G.J. Dolecek, M. Laddomada, Efficient design of two-stage comb-based decimation filters using Chebyshev sharpening, in 2013 IEEE 56th International Midwest Symposium on Circuits and Systems (MWSCAS), pp. 1011–1014 (2013)

Acknowledgements

This work has been carried out in collaboration with Sandhaan Labs Private Limited, Bhubaneswar, India (https://sandhaanlabs.in).

Author information

Authors and Affiliations

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Aggarwal, S., Meher, P.K. Enhanced Sharpening of CIC Decimation Filters, Implementation and Applications. Circuits Syst Signal Process 41, 4581–4603 (2022). https://doi.org/10.1007/s00034-022-01993-w

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-022-01993-w