Abstract

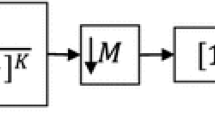

In this paper, we introduce a proper approximation of the amplitude response of a digital filter to the Nth power of a Dirichlet kernel, which allows for the construction of efficient decimation architectures. We present an explicit formula to compute how this approximation affects the worst-case aliasing attenuation in the resulting spectral shape with respect to the exact function, such that the user can identify if the proposed approach is convenient for any given specifications. Additionally, a couple of digital decimation architectures are derived from this approximation. These architectures possess the easy reconfiguration capability of the state-of-the-art Cascaded Integrator-Comb (CIC) exact solution while exhibiting a higher maximum frequency of operation and a reduced utilization of hardware resources without practically affecting power consumption.

Similar content being viewed by others

Data availability statement

Data generated during the current study are available from the corresponding author on reasonable request.

References

A. Abinaya, M. Maheswari, A.S. Alqahtani, Heuristic analysis of CIC filter design for next-generation wireless applications. Arab. J. Sci. Eng. 46, 1257–1268 (2021). https://doi.org/10.1007/s13369-020-05016-1

S. Aggarwal, Improved two-stage decimator structure using Kaiser Hamming sharpening. Circuits Syst. Signal Process. (2020). https://doi.org/10.1007/s00034-020-01592-7

S. Aggarwal, Efficient design of decimation filter using linear programming and its FPGA implementation. Integration 79, 94–106 (2021)

Analog Devices, AD6636 150 MSPS wideband digital downconverter, Data sheet, (2005), Accessed: Feb. 10, 2021. [Online]. Available: https://www.analog.com/media/en/technical-documentation/data-sheets/AD6636.pdf

J. O. Coleman, Chebyshev stopbands for CIC decimation and CIC-implemented array tapers in 1D and 2D. IEEE Trans Circuits Syst. I - Reg. Papers 59(12), 2956–2968 (2012). https://doi.org/10.1109/TCSI.2012.2206435

D. Datta, P. Mitra, H.S. Dutta, FPGA implementation of high performance digital down converter for software defined radio. Microsyst. Technol. (2019). https://doi.org/10.1007/s00542-019-04579-w

A. Dudarin, G. Molnar, M. Vucic, Optimum multiplierless compensators for sharpened cascaded-integrator-comb decimation filters. Electron. Lett. 54(16), 971–972 (2018). https://doi.org/10.1049/el.2018.5114

L. Fa-Long, Digital Front-End in Wireless Communications and Broadcasting: Circuits and Signal Processing, Cambridge University Press, The Edinburgh Building, Cambridge CB2 8RU, UK (2011), ISBN 978-1-107-00213-5

D. Gautam, K. Khare, B.P. Shrivastava, A novel approach for optimal design of sample rate conversion filter using linear optimization technique. IEEE Access (2021). https://doi.org/10.1109/ACCESS.2021.3066292

K.W. Gear, A. Sanchez-Macian, J.A. Maestro, Reduced length redundancy adaptive protection for the cascaded integrator-comb interpolation filter on FPGA. Microelectron. Reliab. (2021). https://doi.org/10.1016/j.microrel.2021.114043

F. Harris, Multirate Signal Processing for Communication Systems, Prentice Hall PTR, Upper Saddle River, New Jersey 07458, USA (2004), ISBN 0-13-146511-2

E. Hogenauer, An economical class of digital filters for decimation and interpolation. IEEE Trans Acoust. Speech Signal Process. 29(2), 155–162 (1981). https://doi.org/10.1109/TASSP.1981.1163535

Intersil, HSP43220 decimating digital filter, Data sheet, (2008), Accessed: Feb. 10, 2021. [Online]. Available: https://media.digikey.com/pdf/Data%20Sheets/Intersil%20PDFs/hsp43220.pdf

Z. Jiang, A.N. Willson, Efficient digital filtering architectures using pipelining/interleaving. IEEE Trans Circuits Syst. II Analog Digital Signal Process. 44(2), 110–119 (1997). https://doi.org/10.1109/82.554438

Q. Jing, Y. Li, J. Tong, Performance analysis of multi-rate signal processing digital filters on FPGA. EURASIP J. Wireless Commun. Netw. (2019). https://doi.org/10.1186/s13638-019-1349-9

J. Kaiser, R. Hamming, Sharpening the response of a symmetric nonrecursive filter by multiple use of the same filter. IEEE Trans Acoust. Speech Signal Proc. (1977). https://doi.org/10.1109/TASSP.1977.1162980

M. Laddomada, Generalized comb decimation filters for sigma-delta AD converters: analysis and design, IEEE Trans. Circuits Syst. I - Reg. Papers 54(5), 994–1005 (2007). https://doi.org/10.1109/TCSI.2007.895528

M. Laddomada, On the polyphase decomposition for design of generalized comb decimation filters, IEEE Trans. Circuits Syst. I - Reg. Papers 55(8), 2287–2299 (2008). https://doi.org/10.1109/TCSI.2008.920136

M. Laddomada, Fixed-point design of generalized comb decimation filters: a statistical approach. IET Signal Process. 4(2), 158–167 (2010). https://doi.org/10.1049/iet-spr.2009.0008

E. Martens et al., RF-to-baseband digitization in 40 nm CMOS with RF bandpass \(\Sigma \)-\(\Delta \) modulator and polyphase decimation filter. IEEE J. Solid State Circuit. 47(4), 990–1002 (2012). https://doi.org/10.1109/JSSC.2012.2185149

U. Meyer-Baese, Digital Signal Processing with Field Programmable Gate Arrays, 4th edn. (Springer, Berlin Heidelberg, 2014). 978-3-642-45308-3

G. Molnar and M. Vucic, Weighted minimax design of sharpened CIC filters, IEEE 20th Internat. Conf. on Electronics, Circuits and Systems (ICECS), Dec. 8-13, Abu Dhabi, United Arab Emirates, pp. 869-872 (2013), https://doi.org/10.1109/ICECS.2013.6815552

G Molnar, A. Dudarin and M. Vucic, Minimax design of multiplierless sharpened CIC filters based on interval analysis, IEEE 39th Internat. Convention on Information and Comm. Technology, Electronics and Microelectronics (MIPRO), May 30-Jun. 3, Opatija, Croatia, pp. 94-98 (2016), https://doi.org/10.1109/MIPRO.2016.7522118

G. Molnar, A. Dudarin, M. Vucic, Design and multiplierless realization of maximally flat sharpened-CIC compensators. IEEE Trans Circuit. Syst. II Express Briefs 65(1), 51–55 (2018). https://doi.org/10.1109/TCSII.2017.2700081

S. Pavan, R. Shcreier and G. C. Temes: Understanding delta-sigma data converters, Wiley, Hoboken, New Jersey, USA (2017), ISBN 978-1-119-25827-8

Renesas, HSP50214B programmable downconverter, Data sheet, (2007), Accessed: Feb. 10, 2021. [Online]. Available: https://www.renesas.com/us/en/document/dst/hsp50214b-datasheet

D. E. Troncoso-Romero, G. Dolecek and M. Laddomada, Design of multiplierless linear phase comb corrector filters for multirate applications, IEEE 3rd Latin American Symp. on Circuits and Systems (LASCAS), Feb. 29–Mar. 2, Playa del Carmen, Mexico, pp.1–4 (2012), https://doi.org/10.1109/LASCAS.2012.6180305

D.E. Troncoso-Romero, M.G. Cruz-Jimenez, Efficient wide-band droop compensation for CIC filters: ad hoc and reconfigurable FIR architectures. Electron. Lett. 53(4), 228–229 (2017). https://doi.org/10.1049/el.2016.3782

P. P. Vaidyanathan, Multirate Systems and Filter Banks, Prentice Hall, Englewood Cliffs, New Jersey 07632, USA (1993), ISBN 0-13-605718-7

L. Zhibin, G. Bo, Y. Ruotong, G. Min, Efficient sharpening CIC filter embedding fifth-order filter with coefficient optimization algorithm. Electron. Lett. 56(23), 1241–1243 (2020). https://doi.org/10.1049/el.2020.1433

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Troncoso Romero, D.E., Cruz Jiménez, M.G. & Meyer-Baese, U. Hardware-Efficient Decimation with Spectral Shape Approximating the Nth Power of a Dirichlet Kernel. Circuits Syst Signal Process 41, 4886–4905 (2022). https://doi.org/10.1007/s00034-022-02009-3

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-022-02009-3