Abstract

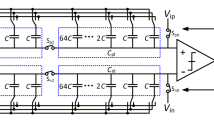

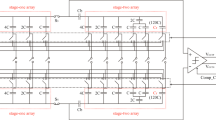

A novel area-efficient capacitor switching scheme for successive approximation register (SAR) analogue-to-digital converters (ADCs) is proposed. By using the charge-sharing and capacitor-holding technique, the proposed switching method achieves deciding the last three least-significant-bits (LSBs) with only two unit capacitors. Additionally, zero power consumption is achieved in the first conversion cycle, and the monotonic switching method is utilized for the remaining cycles. Compared to the conventional structure, the proposed switching scheme reduces the average switching energy by 97.71% and achieves an 87.5% capacitor area reduction without an extra reference voltage or capacitor-splitting structure. A postlayout simulation of a 1-V 10-bit 5-MS/s SAR ADC in 180 nm CMOS technology is performed, which verifies the feasibility of the proposed switching scheme. The SAR ADC achieves a 58.9 dB signal-to-noise and distortion ratio (SNDR) and 72.1 dB spurious-free dynamic range (SFDR).

Similar content being viewed by others

Data Availability

The processed data and material required to reproduce these findings cannot be shared at this time as the data also form part of an ongoing study.

References

L. Chen, A. Sanyal, J. Ma, X. Tang, N. Sun, Comparator common-mode variation effects analysis and its application in SAR ADCs. IEEE Int. Symp. Circuits Syst. (2016). https://doi.org/10.1109/ISCAS.2016.7538972

Y. Chen, Y. Zhuang, H. Tang, A 99.8% energy-reduced two-stage mixed switching scheme for SAR ADC without reset energy. Circuits Syst. Signal Process. 38(12), 5426–5447 (2019). https://doi.org/10.1007/s00034-019-01151-9

B.P. Ginsburg, A.P. Chandrakasan, An energy-efficient charge recycling approach for a SAR converter with capacitive DAC. IEEE Int. Symp. Circuits Syst 43, 184–187 (2005). https://doi.org/10.1109/ISCAS.2005.146455

W. Guo, Z. Zhu, A 0.3 V 8-bit 8.9 fJ/con.-step SAR ADC with sub-DAC merged switching for bio-sensors. Microelectron. J. 68, 44–54 (2017). https://doi.org/10.1016/j.mejo.2017.09.001

L. Huang, L. Zhang, M. Chen et al., A low-energy and area-efficient Vaq-based switching scheme with capacitor-splitting structure for SAR ADCs. Circuits Syst. Signal Process. 40, 4106–4126 (2021). https://doi.org/10.1007/s00034-021-01666-0

P. Lee, C. Kao, C. Hsieh, A 0.4 V 1.94 fJ/conversion-step 10 b 750 kS/s SAR ADC with input-range adaptive-switching. IEEE Int. Symp. Circuits Syst. 14, 1042–1045 (2016). https://doi.org/10.1109/ISCAS.2016.7527422

X. Li, J. Cai, X. Xin et al., High energy-efficient switching scheme for SAR ADC with low common-mode level variation. Analog Integr. Circuits Signal Process. 107, 215–225 (2021). https://doi.org/10.1007/s10470-021-01797-z

C.C. Liu et al., A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE J. Solid-State Circuits 34, 731–740 (2010). https://doi.org/10.1109/JSSC.2010.2042254

C.C. Lu, D.K. Huang, A 10-bits 50-MS/s SAR ADC based on area-efficient and low-energy switching scheme. IEEE Access 8, 28257–28266 (2020)

S.A. Mahmoud, H.A. Salem, H.M. Albalooshi, An 8-bit, 10 KS/s, 1.87 µW successive approximation analog to digital converter in 0.25 µm CMOS technology for ECG detection systems. Circuits Syst. Signal Process. 34, 2419–2439 (2015). https://doi.org/10.1007/s00034-015-9973-z

P. Nuzzo, B.D. Fernando, T. Pieranglo et al., Noise analysis of regenerative comparators for reconfigurable ADC architectures. IEEE Trans. Circuits Syst. I Regul. Pap. 55(6), 1441–1454 (2008). https://doi.org/10.1109/TCSI.2008.917991

D. Osipov, S. Paul, Two advanced energy-back SAR ADC architectures with 99.21 and 99.37% reduction in switching energy. Analog Integr. Circuits Signal Process 87(1), 81–91 (2016)

W. Qu, Z. Zhang, N. Mei, A 99.43% energy saving switching scheme with asymmetric binary search algorithm for SAR ADCs. Circuits Syst. Signal Process. 39(9), 4695–4704 (2020). https://doi.org/10.1007/s00034-020-01383-0

S.U. Rehman, A.M. Kamboh, A CMOS micro-power and area efficient neural recording and stimulation front-end for biomedical applications. Circuits Syst. Signal Process. 34, 1725–1746 (2015). https://doi.org/10.1007/s00034-014-9935-x

B.M. Samaneh, L. Reza, Analysis and design of a low-voltage low-power double-tail comparator. IEEE Trans. Very Large Scale Integr. Syst. 22(9), 1945–1953 (2014). https://doi.org/10.1109/TVLSI.2013.2241799

A. Sanyal, N. Sun, SAR ADC architecture with 98% reduction in switching energy over conventional scheme. Electron. Lett. 49, 248–250 (2013). https://doi.org/10.1049/el.2012.3900

M. Sotoudeh, F. Rezaei, A four-level switching scheme for SAR ADCs with 87.5% area saving and 97.85% energy-reduction. Circuits Syst. Signal Process. 10, 11–12 (2020). https://doi.org/10.1007/s00034-020-01405-x

L.B. Xie et al., Energy-efficient hybrid capacitor switching scheme for SAR ADC. Electron. Lett. 50, 22–23 (2014). https://doi.org/10.1049/el.2013.2794

C. Yuan, Y. Lam, Low-energy and area-efficient tri-level switching scheme for SAR ADC. Electron. Lett. 48, 482–483 (2012). https://doi.org/10.1049/el.2011.4001

Y. Zhang, Y. Li, Z. Zhu, A charge-sharing switching scheme for SAR ADCs in biomedical applications. Microelectron. J. 75, 128–136 (2018). https://doi.org/10.1016/j.mejo.2018.04.003

J. Zhang, Z.M. Zhu, High energy-efficient partial floating capacitor array DAC scheme for SAR ADCs. Analog Integr. Circuits Signal Process. 94(1), 171–175 (2018). https://doi.org/10.1007/s10470-017-1087-z

Y. Zhu et al., A 0.19 mm2 10 b 2.3 GS/s 12-way time-interleaved pipelined-SAR ADC in 65-nm CMOS. IEEE Trans. Circuits Syst. I Regul. Pap. 65(11), 3606–3616 (2018). https://doi.org/10.1109/TCSI.2018.2859027

Y. Zhu et al., A 10-bit 100-MS/s reference-free SAR ADC in 90 nm CMOS. IEEE J. Solid-State Circuits 45, 1111–1121 (2010). https://doi.org/10.1109/JSSC.2010.2048498

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Guo, Y., Qiu, L. & Yao, B. A Highly Area-Efficient Switching Scheme based on Charge Sharing and Capacitor Holding for SAR ADCs. Circuits Syst Signal Process 41, 6561–6580 (2022). https://doi.org/10.1007/s00034-022-02093-5

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-022-02093-5