Abstract

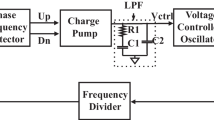

This paper presents a delay-locked loop (DLL) with multiple radiation-hardened techniques. A radiation-hardened charge pump (RH-CP) and a radiation-hardened voltage-controlled delay line (RH-VCDL) are proposed to mitigate effects on DLLs caused by single-event transient (SET). A lock detection module (LDM) is designed in the RH-CP to separate CP and VCDL when the DLL is locked. Thanks to LDM, the voltage transients caused by ion strikes on CP can be prevented from effecting the control voltage of VCDL and causing inverted lock error. A SET correction module (SCM) combined with sliced delay cells is used in the RH-VCDL to select the uncorrupted output and avoid missing pulses errors occurring at the output of DLL. The proposed DLL is designed in 22-nm CMOS process with an operation frequency of 5 GHz. Simulations at linear energy transfer (LET) between 40 and 100 MeV-cm2/mg show that RH-CP eliminates inverted lock error and RH-VCDL mitigates missing pulses generated by the DLL after ion strikes effectively.

Similar content being viewed by others

Explore related subjects

Discover the latest articles and news from researchers in related subjects, suggested using machine learning.Data Availability

The datasets generated during and/or analysed during the current study are available from the corresponding author on reasonable request.

References

S. Dong, X. Tong, L. Liu, A. Yang, R. Li, A gain & bandwidth reprogrammable neural recording amplifier with leakage reduction switches. 2019 IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC), 1–3 (2019)

Y. Feng, Q. Fan, Y. Tang, Z. Zuo, J. Chen, A radiation-tolerant DLL with fine resolution and duty cycle corrector for memory interface. IEEE DCAS, 1–5 (2016)

S. Hoyos, C.W. Tsang, J. Vanderhaegen, Y. Chiu, Y. Aibara, H. Khorramabadi, B. Nikolic, A 15 MHz to 600 MHz, 20 mW, 0.38 mm2 split-control, fast coarse locking digital DLL in 01.3 um CMOS. IEEE Trans. Very Large Scale Integr. VLSI Syst. 20, 564–568 (2015)

M.-H. Hsieh, L.-H. Chen, S.-I. Liu, C. Chung-Ping Chen, A 6.7 MHz to 1.24 GHz 00318 mm2 fast-locking all-digital DLL using phase-tracing delay unit in 90 nm CMOS. IEEE J. Solid-State Circuits. 51, 412–426 (2016)

H.-W. Lee, C. Kim, Survey and analysis of delay-locked loops used in DRAM interfaces. IEEE Trans. Very Large Scale Integr. VLSI Syst. 22, 701–711 (2014)

Y. Li, Y. Guo, C. He, J. Liu, Y. Li, P. Li, Simulation studies on the transient dose rate effect of analog delay locked loops. Microelectron. Reliab. 121, 1–11 (2021)

P. Maillard et al., An RHBD technique to mitigate missing pulses in delay locked loops. IEEE Trans. Nucl. Sci. 57, 3634–3639 (2010)

P. Maillard et al., A new error correction circuit for delay locked loops. IEEE Trans. Nucl. Sci. 60, 4387–4393 (2013)

P. Maillard, W. Timothy Holman, T. Daniel Loveless, L.W. Massengill, A radiation-hardened delay-locked loop (DLL) utilizing a differential delay line topology. IEEE RADECS 5, 675–682 (2011)

S. Park, J. Kim, C. Hwang, H. Park, S. Yoo, T. Seong, J. Choi, A 01–15-GHz wide harmonic-locking-free delay-locked loop using an exponential DAC. IEEE Microw. Wireless Compon. Lett. 29, 548–550 (2019)

K.R. Pasupathy, B. Bindu, A review on circuit simulation techniques of single-event transients and their propagation in delay locked loop. IETE Tech. Rev. 34, 276–285 (2017)

S.U. Rehman et al., A 0.2–1.3 ns range delay-control scheme for a 25 Gb/s data-receiver using a replica delay-line-based delay-locked-loop in 45-nm CMOS. IEEE Trans. Circuits Syst. II Exp. Briefs 67, 806–810 (2020)

K. Ryu, D.-H. Jung, S.-O. Jung, A DLL with dual edge triggered phase detector for fast lock and low jitter clock generator. IEEE Trans. Circuits Syst. I: Reg. Papers 59, 1860–1870 (2012)

R. Sengupta, B. Vermeire, L.T. Clark, B. Bakkaloglu, A 133 MHz radiation-hardened delay-locked loop. IEEE Trans. Nucl. Sci. 57, 3626–3633 (2010)

S. Yang, D. Huang, X. Wen, L. Chen, J. Chen, A radiation-hardened DLL with fine resolution and DCC for DDR2 memory interface in 0.13 um CMOS. IEEE ISCAS 56, 1496–1499 (2013)

Z. Zhenyu et al., A single-event transient hardened phase-locked loop in 0.18 μm CMOS process. IEEE ASICON, 284–287 (2009)

Acknowledgements

This work is supported by the China Scholarship Council (CSC) (Project No.: 202006960020).

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Chen, Y., Zhuang, Y. Analysis and Design of a Delay-Locked Loop with Multiple Radiation-hardened Techniques. Circuits Syst Signal Process 42, 130–146 (2023). https://doi.org/10.1007/s00034-022-02151-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-022-02151-y