Abstract

This work presents a technique to increase the output voltage swing of CMOS current mirrors which comprise stacked devices in their output branches, here generally referred as cascode current mirrors. The technique consists in replacing the primary output transistor by a network of four devices designed to anticipate the saturation onset. In such way, the cascode current mirror attains a reasonably higher-voltage compliance at its output, preserving other desirable features such as low output conductance and low mirroring error. The frequency bandwidth and power are not significantly affected. Simulation results on a 130-nm CMOS technology with 1.2-V supply voltage corroborate these observations: The increase in output voltage swing is within fifty to one hundred millivolts, while the increase in area is within 10–50% depending on circuit topology. This increase in area is much less than the resulting increase from re-dimensioning the circuit without the LSOT to achieve similar output voltage swing.

Similar content being viewed by others

Data Availability

The datasets generated during and/or analyzed during the current study are available from the corresponding author on reasonable request.

Code Availability

No code has been generated during the current study.

Notes

In this context earlier means at lower VDS magnitude.

References

B. Aggarwal, M. Gupta, A.K. Gupta, A comparative study of various current mirror configurations: topologies and characteristics. Microelectron. J. 53, 134–155 (2016). https://doi.org/10.1016/j.mejo.2016.04.015

B. Aggarwal, M. Gupta, H. Malik, M. Garg, G. Taneja, A new high output resistance accurate CMOS current mirror, in Advances in Energy Technology. Lecture Notes in Electrical Engineering, vol. 766, ed. by R.C. Bansal, A. Agarwal, V.K. Jadoun (Springer, Singapore, 2022). https://doi.org/10.1007/978-981-16-1476-7_1

B. Aggarwal, Novel current mirrors based on folded flipped voltage follower configuration. Wirel. Pers. Commun. 123, 645–653 (2022). https://doi.org/10.1007/s11277-021-09150-3

E. Arslan, Self-biasing high precision CMOS current subtractor for current-mode circuits. Adv. Electr. Comput. Eng. 13(4), 19–24 (2013). https://doi.org/10.4316/AECE.2013.04004

C.W.V. Casañas, T.H.P. de Castro, G.A.F. de Souza, R.L. Moreno, D.M. Colombo, A review of CMOS current references. J. Integr. Circuits Syst. (2022). https://doi.org/10.29292/jics.v17il.592

N. Domala, G. Sasikala, Low power flipped voltage follower current mirror with improved input output impedances. Sãdhanã 46, 142 (2021). https://doi.org/10.1007/s12046-021-01665-6

E.S. dos Santos, F.S. de Andrade, M.D. Pereira, A.I. Araújo Cunha, Improvements on the Design of the low saturation onset transistor, in Proceedings of the 2020 27th IEEE International Conference on Electronics, Circuits and Systems. ICECS, (2020), pp. 1–4. https://doi.org/10.1109/ICECS49266.2020.9294977

C.C. Enz, F. Krummenacher, E.A. Vittoz, An analytical MOS transistor model valid in all regions of operation and dedicated to low voltage and low-current applications. Analog Integr. Circuits Signal Process. 8, 83–114 (1995). https://doi.org/10.1007/BF01239381

A.A. Fernandes, F.S. de Andrade, A.J.S. de Sousa, G.C. Gonçalves, E.P. Santana, M.D. Pereira, A.I.A. Cunha, Low saturation onset MOS transistor: an equivalent network, in Proceedings of the 2019 34th Symposium on Microelectronics Technology and Devices. SBMicro (2019), pp. 1–4. https://doi.org/10.1109/SBMicro.2019.8919312

M. Gupta, B. Aggarwal, A.K. Gupta, A very high performance self-biased cascode current mirror for CMOS technology. Analog Integr. Circuits Signal Process. 75, 67–74 (2013). https://doi.org/10.1007/s10470-012-9994-5

K.R. Laker, W.M.C. Sansen, Design of Analog Integrated Circuits and Systems (McGraw-Hill Education, New York, 1994)

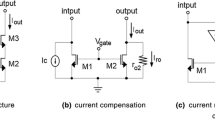

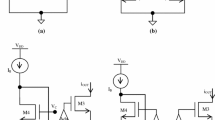

S. Leitner, H. Wang, Current compensation techniques for low-voltage high-performance current mirror circuits. Analog Integr. Circuits Signal Process. 88(1), 79–88 (2016). https://doi.org/10.1007/s10470-016-0743-z

M.H. Maghami, A.M. Sodagar, M. Sawan, Analysis and design of a high-compliance ultra-high output resistance current mirror employing positive shunt feedback. Int. J. Circuit Theory Appl. 43(12), 1935–1952 (2015). https://doi.org/10.1002/cta.2049

K. Monfaredi, H. Faraji Baghtash, An extremely low-voltage and high-compliance current-mirror. Circuits Syst. Signal Process. 39, 30–53 (2020). https://doi.org/10.1007/s00034-019-01175-1

M. Quarantelli, M. Poles, M. Pasotti, P. Rolandi, A high compliance CMOS current source for low voltage applications, in Proceedings of the 2003 International Symposium on Circuits and Systems. ISCAS '03, (2003), pp. I-I. https://doi.org/10.1109/ISCAS.2003.1205591

S.S. Rajput, P. Vajpayee, G.K. Sharma, 1V high performance current mirror for low voltage analog and mixed signal applications in submicron regime, in Proceedings of the 2009 IEEE Region 10 Conference. TENCON, (2009), pp. 1–4. https://doi.org/10.1109/TENCON.2009.5396113

J. Ramirez-Angulo, R.G. Carvajal, A. Torralba, Low supply voltage high-performance CMOS current mirror with low input and output voltage requirements. IEEE Trans. Circuits Syst. II Express Br. 51(3), 124–129 (2004). https://doi.org/10.1109/TCSII.2003.822429

S. Sabharwal, J. Kaur, A. Shahi, Various current mirror topologies: a survey, in Proceedings of the 2022 2nd International Conference on Advance Computing and Innovative Technologies in Engineering. ICACITE, (2022), pp. 504–508. https://doi.org/10.1109/ICACITE53722.2022.9823824

E. Sackinger, W. Guggenbuhl, A high-swing, high-impedance MOS cascode circuit. IEEE J. Solid-State Circuits 25(1), 289–298 (1990). https://doi.org/10.1109/4.50316

M.C. Schneider, C. Galup-Montoro, CMOS Analog Design Using All-Region MOSFET Modeling (Cambridge University Press, Cambridge, 2010)

E. Seevinck, M. Du Plessis, T.-H. Joubert, A.E. Theron, Active-bootstrapped gain-enhancement technique for low-voltage circuits. IEEE Trans. Circuits Syst. II Analog Digit. Signal Process. 45(9), 1250–1254 (1998). https://doi.org/10.1109/82.718592

T. Serrano, B. Linares-Barranco, The active-input regulated-cascode current mirror. IEEE Trans. Circuits Syst. I Fundam. Theory Appl. 41(6), 464–467 (1994). https://doi.org/10.1109/81.295247

A.J.S. Sousa, F.S. Andrade, M.A.M. Bomfim, A.S. Silva, H.C. Santos, R.N. Lima, E.P. Santana, A.I.A. Cunha, Compact CMOS analog multiplier free of voltage reference generators. J. Integr. Circuits Syst. 14(3), 1–12 (2020). https://doi.org/10.29292/jics.v15i3.139

K. Tanno, O. Ishizuka, Z. Tang, Four-quadrant CMOS current-mode multiplier independent of device parameters. IEEE Trans. Circuits Syst. II Analog Digit. Signal Process. 47(5), 473–477 (2000). https://doi.org/10.1109/82.842116

E. Tiiliharju, S. Zarabadi, M. Ismail, K. Halonen, A very-high impedance, high-swing cascode stage for sub-micron analog VLSI. IEEE Circuits Devices Mag. 13(4), 49–50 (1997). https://doi.org/10.1109/101.600710

Y. Tsividis, Operation and Modeling of the MOS Transistor (Oxford University Press, Cambridge, 2003)

M.A. Valencia-Ponce, P.R. Castañeda-Aviña, E. Tlelo-Cuautle, V.H. Carbajal-Gómez, V.R. González-Díaz, Y. Sandoval-Ibarra, J.-C. Nuñez-Perez, CMOS OTA-based filters for designing fractional-order chaotic oscillators. Fractal Fract. 5(3), 122 (2021). https://doi.org/10.3390/fractalfract5030122

M.A. Valencia-Ponce, E. Tlelo-Cuautle, L.G. de la Fraga, On the sizing of CMOS operational amplifiers by applying many-objective optimization algorithms. Electronics 10(24), 3148 (2021). https://doi.org/10.3390/electronics10243148

A.D. Vidhate, S. Suman, Low power high performance current mirror: a review. J. Phys. Conf. 1804, 012161 (2021). https://doi.org/10.1088/1742-6596/1804/1/012161

H. Xie, Z. Wang, G. Liu, J. Lu, X. Yi, A novel active-input cascode current mirror with high precision and low power dissipation. Eng. Rep. 4(2), e12451 (2021). https://doi.org/10.1002/eng2.12451

F. You, H.K. Embabi, J.F. Duque-Carrillo, E. Sanchez-Sinencio, An improved tail current source for low voltage applications. IEEE J. Solid-State Circuits 32(8), 1173–1180 (1997). https://doi.org/10.1109/4.604073

Acknowledgements

Authors would like to acknowledge Conselho Nacional de Desenvolvimento Científico e Tecnológico—CNPq, Coordenação de Aperfeiçoamento de Pessoal de Nível Superior—CAPES, Fundação de Amparo à Pesquisa do Estado da Bahia—FAPESB and Sociedade Brasileira de Microeletrônica—SBMicro for the financial support.

Funding

This work received financial support from: Conselho Nacional de Desenvolvimento Científico e Tecnológico—CNPq, Coordenação de Aperfeiçoamento de Pessoal de Nível Superior—CAPES, Fundação de Amparo à Pesquisa do Estado da Bahia—FAPESB and Sociedade Brasileira de Microeletrônica—SBMicro.

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

There are no conflicts of interest or competing interests.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Appendices

Appendix A

In CMOS technologies that use either LOCOS or STI as isolation techniques, charge sharing due to narrow widths affects the MOSFET threshold and saturation onset [26]. Therefore, the drain current variations with drain-to-source voltage are slightly different in MOS transistors with equal terminal voltages and equal lengths but with different widths. The ratio between their currents may even exhibit significant variation at low drain-to-source voltages. To illustrate this issue, we have simulated the DC output characteristics of several MOS transistors from a 130-nm CMOS technology, connected by the drain, source, gate and bulk terminals. The ratios between the drain currents of the pairs of transistors with equal channel lengths and different channel widths are depicted in Fig.

Simulated normalized drain current ratios versus drain-to-source voltage VDS, for pairs of MOS transistors with: channel widths W1 = 2.00 µm and W2 = 20.00 µm (black lines); W1 = 2.00 µm and W2 = 0.20 µm (red lines); W1 = 0.20 µm and W2 = 20.00 µm (blue lines); channel length L = 0.12 µm (solid lines); channel length L = 2.00 µm (dashed lines). For all transistors: gate potential VG = 0.6 V, source and bulk potentials VS = VB = 0, drain terminals connected. Normalization constant: M = W2/W1 for each pair of transistors. Simulation software: SMASH; model: BSIM3v3; CMOS technology node: 130 nm

9. These current ratios have been normalized by the ratio M between the MOSFET aspect ratios of each pair.

Appendix B

To verify whether the introduction of the LSOT network in the cascode mirror and in the RCCM contributes to improve output voltage compliance at lower supply voltages, DC output characteristics of the current mirrors with the sizes of Table 3 have been simulated for supply voltages between 1.2 and 0.8 V (reductions of up to 33%). In the cascode mirrors and LSOT-CM, it was not possible to properly dimension a simple current source able to provide the input current value of 10 µA at the mirror input for the constrained voltage room of 0.8 V. Hence the minimum supply voltage adopted in these cases was 0.9 V.

A similar verification has been accomplished for temperature deviations from the standard value of 27 °C. Thus, the DC output characteristics of the five configurations of cascode mirrors, LSOT-CM, RCCM and LSOT-RCCM have been simulated for temperatures of − 40 °C and 100 °C.

The results concerning the current mirrors with and without LSOT are compared through Fig.

10, for supply voltage variation, and through Fig.

11, for temperature variation, which present: (a) the differences between the values of vOUTmin without and with LSOT, (b) the ratios between the mean values of output conductance gOUT with and without LSOT and (c) the ratios between the mean values of mirroring error ε without and with LSOT. The mean values of gOUT and ε have been computed for the values of vOUT in the range between VDD/2 and VDD.

As can be seen in Fig. 10a, despite the reduction of the supply voltage, the differences between the values of vOUTmin without and with LSOT are positive, indicating that the substitution of the output primary transistor in the cascode mirror and in the RCCM promotes reduction of the minimum output voltage. Nevertheless, the lower the supply voltage smaller the voltage reduction. In Fig. 10b, the ratio between the mean values of output conductance gOUT with and without LSOT decreases, showing that the mean value of gOUT, in turn, becomes still smaller with LSOT application as supply voltage diminishes. In Fig. 10c, the comparison between RCCM and LSOT-RCCM shows a trend of error degradation with LSOT application as supply voltage is lowered, but no trend is observable in the comparison between cascode mirror and LSOT-CM.

In Fig. 11a, b, for both cascode mirror and RCCM, the LSOT application slightly improves vOUTmin and output conductance for all tested temperatures and more emphatically as temperature augments. The opposite behavior is verified for the mirroring error in Fig. 11c, except for the cascode mirror with 1-µA input current and mirror ratio M = 100.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Fernandes, A.A., dos Santos, E.S., Simões, M.M.C. et al. Improving Output Voltage Swing in Cascode Current Mirrors. Circuits Syst Signal Process 42, 3268–3291 (2023). https://doi.org/10.1007/s00034-023-02293-7

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-023-02293-7