Abstract

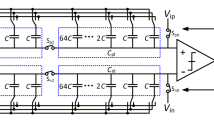

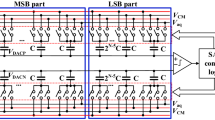

A high energy-efficient and reference voltage self-adaptive switching scheme for a triple-capacitive array successive approximation register analog-to-digital converters is proposed. The proposed switching time scheme includes Bi-level and Tri-level modes. The operating mode can be automatically switched by the reference voltage self-adaptive module according to the number of reference voltages of the peripheral circuits. The proposed timing scheme has the advantage of automatic compatibility with Bi/Tri-level reference voltage, which can be better adapted to the requirements of different hybrid ADC architectures. In Bi/Tri-level mode, two-step method, and monotonic switching scheme, floating capacitor technology is used to achieving 99.6% and 99.9% savings in average switching energy and a 73.4% reduction in total capacitance compared to the conventional scheme when applied to a 10-bit SAR ADC. The INL and DNL for both the Bi-level reference mode and the Tri-level reference mode are 0.350, 0.347 and 0.177, 0.172, respectively. In addition, the scheme eliminates to reset energy while regulating M to achieve a compromise between energy, area, and linearity. The post-simulation results show that the 10-bit SAR ADC with the proposed switching scheme can achieve a signal-to-noise distortion ratio (SNDR) of 60.53 dB and a spurious-free dynamic range (SFDR) of 68 dB at a sampling rate of 20 MS/s in a 65 nm CMOS process. The area of this ADC is only 0.2392 mm2.

Similar content being viewed by others

Data availability

Data sharing is not applicable to this article as no datasets were generated or analyzed during the current study.

References

S. Baek, K. Lee, M. Lee, Energy-efficient switching scheme for SAR ADC using zero-energy dual capacitor switching. Analog Integr. Circ. Sig. Process 94(4), 317–322 (2018). https://doi.org/10.1007/s10470-017-1101-5

J. Borgmans, E. Sacco, P. Rombouts, G. Gielen, Methodology for readout and ring oscillator optimization toward energy-efficient VCO-based ADCs. IEEE Trans. Circ. Syst. I Regul. Pap. 69(3), 985–998 (2022). https://doi.org/10.1109/TCSI.2021.3129919

T.T. Chen, J.P. Cai, High-efficient two-step switching scheme for SAR ADC with dual-capacitive arrays and four-input comparator. Analog Integr. Circ. Sig. Process 101(4), 363–373 (2019). https://doi.org/10.1007/s10470-019-01536-5

Y.S. Chen, Y.Q. Zhuang, A 99.8% energy-reduced two-stage mixed switching scheme for SAR ADC without reset energy. Circuits Systems Signal Process. 38(04), 5426–5447 (2019). https://doi.org/10.1007/s00034-019-01151-9

L. Ding, S.X. Dong, S.J. Liu, A novel split capacitor array switching scheme with proportional coefficient for SAR ADC. Analog Integr. Circ. Sig. Process 98(4), 597–605 (2019). https://doi.org/10.1007/s10470-018-1373-4

R. Ding, L. Dang, H. Lin, D. Sun, S. Liu, Z. Zhu, A 7b 400 MS/s pipelined SAR ADC in 65 nm CMOS. Microelectron. J. 95(3), 0026–2692 (2020). https://doi.org/10.1016/j.mejo.2019.104680

R.X. Ding, D.P. Sun, Shubin Liu, Energy-efficient switching scheme based on floating technique for SAR ADC. Analog Integr. Circ. Sig. Process 97(9), 115–122 (2018). https://doi.org/10.1007/s10470-018-1242-1

A. Gusev, D. Osipov, S. Paul, An energy efficient SAR ADC architecture with DAC Separation. IEEE International New Circuits and Systems Conference (NEWCAS) pp 118–121 (2020). Doi: https://doi.org/10.1109/NEWCAS49341.2020.9159764.

J. Huang, J. Wu, A. Wu, Two-step Vcm-based MS switching method with dual-capacitive arrays for SAR ADCs. Analog Integr. Circ. Sig. Process 94(9), 155–160 (2018). https://doi.org/10.1007/s10470-017-1082-4

L. Huang, L. Zhang, M. Chen, J. Li, J. Wu, A low-energy and area-efficient vaq-based switching scheme with capacitor-splitting structure for SAR ADCs. Circuits Syst. Signal Process. 40(12), 4106–4126 (2021). https://doi.org/10.1007/s00034-021-01666-0

Y. Huang, L.L. Huang, J.H. Wu, An energy-efficient switching scheme based on the improved semi-resting DAC structure and floating-capacitor technique for SAR ADC. Analog Integr. Circ. Sig. Process 108(4), 679–687 (2021). https://doi.org/10.1007/s10470-021-01910-2

B. Jajodia, A. Mahanta, S. Ahamed, Energy-efficient DAC switching technique for single-ended SAR ADCs. Microelectron. J. 124, 1434–8411 (2022). https://doi.org/10.1016/j.aeue.2020.153334

W. Jin, K. Pun, A DEM-free sturdy MASH delta-sigma modulator with a highly-linear tri-level DAC. In: IEEE International Conference on Electron Devices and Solid-State Circuits (EDSSC) pp. 1–2 (2019). doi: https://doi.org/10.1109/EDSSC.2019.8754500

X. Jin, H. Pan, F. Foster, A dual-residue pipelined SAR ADC using only zero-crossing signals. Analog Integr. Circ. Sig. Process 108(12), 229–239 (2021). https://doi.org/10.1007/s10470-021-01860-9

J. Li, X. Li, L. Huang, J. Wu, An energy-efficient switching scheme with low common-mode voltage variation and no-capacitor-splitting DAC for SAR ADC. Analog Integr. Circ. Sig. Process 104(4), 93–101 (2020). https://doi.org/10.1007/s10470-020-01661-6

X.Y. Li, J.S. Li, Low-power switching scheme with quarter reference voltage sources for SAR ADCs. J. Electromagnet. Eng. Sci. 22(2), 129–137 (2022). https://doi.org/10.26866/jees.2022.2.r.69

C.C. Liu, S. Chang, G.Y. Huang, Y.Z. Lin, A 10-bit 50-MS/s SAR ADC with a monotonic capacitor switching procedure. IEEE J. Solid-State Circuits 45(4), 731–740 (2010). https://doi.org/10.1109/JSSC.2010.2042254

Y. Lu, T. Zhou, J. Huang, L. Wang, M. Chen, Y. Li, MSB-split VCM-based charge recovery symmetrical switching with set-and-down asymmetrical switching method for dual-capacitive arrays SAR ADC. Analog Integr. Circ. Sig. Process 106(4), 669–681 (2021). https://doi.org/10.1007/s10470-020-01789-5

J. Luo, Y. Liu, J. Li et al., A low voltage and low power 10-bit Non-Binary 2b/Cycle time and voltage based SAR ADC. IEEE Trans. Circuits Syst. I Regul. Pap. 67(4), 1136–1148 (2020). https://doi.org/10.1109/TCSI.2019.2949072

M. Momeni, M. Yavari, Shifting the sampled input signal in successive approximation register analog-to-digital converters to reduce the digital-to-analog converter switching energy and area. Int. J. Circuit Theory Appl. 48(11), 1873–1886 (2020). https://doi.org/10.1002/cta.2852

E. Rahimi, M. Yavari, Energy-efficient high-accuracy switching method for SAR ADCs. Electron. Lett. 50(7), 499–501 (2014). https://doi.org/10.1049/el.2013.3451

A. Rasool, M. Saberia, R. Lotfi, A low-power capacitor switching scheme with low common-mode voltage variation for successive approximation ADC. Microelectron. J. 61, 0026–2692 (2017). https://doi.org/10.1016/j.mejo.2016.12.009

B. Rikan, H. Abbasizadeh, Y. Park, A 10-bit 1 MS/s segmented Dual-Sampling SAR ADC with reduced switching energy. Microelectron. J. 70, 0026–2692 (2017). https://doi.org/10.1016/j.mejo.2017.11.005

M. Sotoudeh, F. Rezaei, A four-level switching scheme for SAR ADCs with 87.5% area saving and 97.85% energy-reduction. Circuits Syst. Signal Process. 39, 4792–4809 (2020). https://doi.org/10.1007/s00034-020-01405-x

X. Tang, M.M. Song, Y. Chen, A 10-Bit 120 kS/s SAR ADC without reset energy for biomedical electronics. Circuits Systems Signal Process. 38(4), 5411–5425 (2019). https://doi.org/10.1007/s00034-019-01138-6

Y. Tang, W.P. Zhang, C.S. Li, Low-energy and area-efficient switching scheme for SAR A/D converter. Analog Integr. Circ. Sig. Process 80(1), 153–157 (2014). https://doi.org/10.1007/s10470-014-0300-6

X.Y. Tong, M. Zhao, X. Xin, High energy efficiency and linearity switching scheme without reset energy for SAR ADC. Circuits Syst. Signal Process. (2022). https://doi.org/10.1007/s00034-022-02038

H. Wang, Vaq-assisted low-power capacitor-splitting switching scheme for SAR ADCs. Circuits Syst. Signal Process. (2022). https://doi.org/10.1007/s00034-022-02097-1

A.D. Wu, J.H. Wu, Energy-efficient switching scheme for ultra-low voltage SAR ADC. Analog Integr. Circ. Sig. Process 90(2), 507–511 (2017). https://doi.org/10.1007/s10470-016-0892-0

L.B. Xie, G.J. Wen, J.X. Liu, Y. Wang, Energy-efficient hybrid capacitor switching scheme for SAR ADC. Electron. Lett. 50(1), 22–23 (2014). https://doi.org/10.1049/el.2013.2794

Y. Xie, Y. Liang, M. Liu, S. Liu, Z. Zhu, A 10-Bit 5 MS/s VCO-SAR ADC in 0.18- m CMOS. IEEE Trans. Circuits Syst. II Express Briefs 66(1), 26–30 (2019). https://doi.org/10.1109/TCSII.2018.2833866

T. Yousefi, A. Dabbaghian, M. Yavari, An energy-efficient DAC switching method for SAR ADCs. IEEE Trans. Circuits Syst. II Express Briefs 65(1), 41–45 (2018). https://doi.org/10.1109/TCSII.2017.2676048

C. Yuan, Low-energy and area-efficient tri-level switching scheme for SAR ADC. Electron. Lett. 48(9), 482–483 (2012). https://doi.org/10.1049/el.2011.4001

H.S. Zhang, H. Zhang, R.Z. Zhang, Energy-efficient higher-side-reset-and-set switching scheme for SAR ADC. Electron. Lett. 53(18), 1238–1240 (2017). https://doi.org/10.1049/el.2017.2186

Y. Zhu, Z.H. Chen, S.R. Xin, A 10-bit 100-MS/s reference-free SAR ADC in 90 nm CMOS. IEEE J. Solid-State Circuits 45(6), 1111–1121 (2010). https://doi.org/10.1109/JSSC.2010.2048498

Z.M. Zhu, X. Yu, X.L. Song, VCM-based monotonic capacitor switching scheme for SAR ADC. Electron. Lett. 49(5), 327–329 (2013). https://doi.org/10.1049/e1.2012.3332

Acknowledgements

This work was supported by the National Natural Science Foundation of China (61804124), the Natural Science Basic Research Plan in Shaanxi Province of China (2021JQ-718).

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Appendix: Without Reset Energy Consumption of Eqs. (16)–(33)

Appendix: Without Reset Energy Consumption of Eqs. (16)–(33)

The reset energy consumption of the proposed Bi-level reference voltage capacitor switching structure is shown in the following mathematical derivation.

The value of the VFP2 voltage changed and the energy consumed by the voltage flip for this process is zero, as evidenced by the following equation:

The value of the voltage changes of VCP2 and the energy consumed by the voltage flip as shown in (19):

The value of the voltage changes of VFN2 and the energy consumed is:

The value of the voltage changes of VCN2 and the energy consumed by the voltage flip is proved and is calculated below:

Thus, the total energy consumption of the Bi-level reference voltage scheme is:

The reset energy consumption of the proposed Tri-level reference voltage capacitor switching structure is calculated by the following equation.

The value of the VFP2 voltage changed and the energy consumed by the voltage flip for this process is zero, as evidenced by the following mathematical derivation:

The value of the voltage changes of VCP2 and the energy consumed by the voltage flip is proved by the following equation:

The value of the voltage changes of VFN2 and the energy consumed by the voltage flipped is proved and calculated below:

The value of the voltage changes of VCN2 and the energy consumed by the voltage flipped is proved by the following expression:

The total energy consumption of the Tri-level-based voltage scheme is:

Conclusion: The proposed Bi-level reference voltages and Tri-level reference voltages have no reset energy consumption. The analysis shows that there is no switch to the ports of the capacitor array and the comparator and that the voltage of each capacitor on the bottom plate of the capacitor array is not consistent. This will exist to reset the energy consumption.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Dong, S., Liu, C., Bu, S. et al. A Bi/Tri-level Self-Adaptive Two-Step DAC Switching Scheme for High-Power Efficiency SAR-Based ADCs. Circuits Syst Signal Process 42, 4470–4505 (2023). https://doi.org/10.1007/s00034-023-02352-z

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-023-02352-z