Abstract

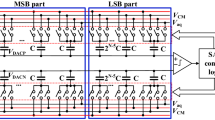

An 11-bit, power efficiency, two-stage SAR-voltage-controlled oscillator (VCO) hybrid ADC is proposed in this work. Taking full advantage of the voltage-to-phase and voltage-to-frequency characteristics, the reused ring-VCO circuit acts as not only a time-domain comparator with the phase detector assistance for low power consumption in the first SAR stage but also a fine quantizer in the second stage. More importantly, the gain nonlinearity of the VCO can be effectively suppressed due to the small residue voltage after the coarse quantization. In addition, the VCO-based ADC (except for the ring-VCO circuit) only works in the quantization phase instead of the whole conversion period. As a result, the power consumption and area of the comparator in the previous SAR-VCO ∆Σ ADC can be thoroughly avoided. Besides, compared to an 11-bit SAR ADC, the capacitor mismatch can be relaxed theoretically by 2 × in the identical capacitor array area. Post-simulation results demonstrate that the proposed ADC in a 0.18 μm CMOS process exhibits a signal-to-noise and distortion ratio (SNDR) of 63.8 dB, and it dissipates 2.1 μW power from a 0.6 V supply with a sampling rate of 50 kS/s and a Nyquist input rate. To the author's knowledge, the hybrid ADC can achieve the best Walden figure of merit (FoMw) of 33.3 fJ/conversion-step compared with the previous SAR-VCO hybrid ADC, and its active area is only 0.109 mm2.

Similar content being viewed by others

Data Availability

Date sharing is not applicable to this article as no datasets were generated or analyzed during the current study.

References

I. Bhattacharjee, G. Chowdary, A 0.45 mV/V line regulation, 0.6 V output voltage, reference-integrated, error amplifier-less LDO with a 5-transistor regulation core. IEEE J. Solid-State Circuits (2023). https://doi.org/10.1109/JSSC.2023.3279669

Z. Ding, X. Zhou, Q. Li, A 0.5–1.1-V adaptive bypassing SAR ADC utilizing the oscillation-cycle information of a VCO-based comparator. IEEE J. Solid-State Circuits 54(4), 968–977 (2019). https://doi.org/10.1109/JSSC.2018.2885554

A. Gupta, K. Nagaraj, T. Viswanathan, A two-stage ADC architecture with VCO-based second stage. IEEE Trans. Circuits Syst. II Express Briefs 58(11), 734–738 (2011). https://doi.org/10.1109/TCSII.2011.2168015

S. Hsieh, C. Kao, C. Hsieh, A 0.5-V 12-bit SAR ADC using adaptive time-domain comparator with noise optimization. IEEE J. Solid-State Circuits 53(10), 2763–2771 (2018). https://doi.org/10.1109/JSSC.2018.2862880

W. Huang, S. Liu, Sub-1 V capacitor-free low-dropout regulator. Electron. Lett. 42(24), 1395–1396 (2006). https://doi.org/10.1049/el:20062871

M. Hu, J. Jin, Y. Guo et al., A power-efficient SAR ADC with optimized timing-redistribution asynchronous SAR logic in 40-nm CMOS. Circuits Syst. Signal Process. 40, 3125–3142 (2021). https://doi.org/10.1007/s00034-020-01643-z

M. Jian, J. Zheng, X. Kong et al., A 12-bit SAR ADC with a reversible VCM-based capacitor switching scheme. Microelectron. J. 129, 105588 (2022). https://doi.org/10.1016/j.mejo.2022.105588

J. Kim, T. Jang, Y. Yoon et al., Analysis and design of voltage-controlled oscillator based analog-to-digital converter. IEEE Trans. Circuits Syst. I Regul. Pap. 57(1), 18–30 (2010). https://doi.org/10.1109/TCSI.2009.2018928

S. Lee, S. Park, H. Park et al., A 21 fJ/conversion-step 100 kS/s 10-bit ADC with a low-noise time-domain comparator for low-power sensor interface. IEEE J. Solid-State Circuits 46(3), 651–659 (2011). https://doi.org/10.1109/JSSC.2010.2102590

H. Li, Y. Shen, E. Cantatore et al., Small-area SAR ADCs with a compact unit-length DAC layout. IEEE Trans. Circuits Syst. II Express Briefs 69(10), 4038–4042 (2022). https://doi.org/10.1109/TCSII.2022.3186064

S. Li, A. Mukherjee, N. Sun, A 174.3-dB FoM VCO-based CT ∆Σ modulator with a fully-digital phase extended quantizer and tri-level resistor DAC in 130-nm CMOS. IEEE J. Solid-State Circuits 52(7), 1940–1952 (2017). https://doi.org/10.1109/JSSC.2017.2693244

Y. Luo, M. Ortmanns, Input referred noise of VCO-based comparators. IEEE Trans. Circuits Syst. II Express Briefs 68(1), 82–86 (2021). https://doi.org/10.1109/TCSII.2020.3008260

M. Momeni, M. Yavari, Shifting the sampled input signal in successive approximation register analog-to-digital converters to reduce the digital-to-analog converter switching energy and area. Int. J. Circuit Theory Appl. 48(11), 1873–1886 (2020). https://doi.org/10.1002/cta.2852

C.-C. Peng, T. Chu, A 10.7b 300MS/s Two-step digital-slope ADC in 65 nm CMOS. IEEE Trans. Circuits Syst. I: Regul. Papers 67(9), 2948–2959 (2020). https://doi.org/10.1109/TCSI.2020.2987697

F. Pepe, P. Andreani, An accurate analysis of phase noise in CMOS ring oscillators. IEEE Trans. Circuits Syst. II Express Briefs 66(8), 1292–1296 (2019). https://doi.org/10.1109/TCSII.2018.2884569

Ó. Pereira-Rial, P. López, J. Carrillo, 0.6-V-VIN 7.0-nA-IQ 0.75-mA-IL CMOS capacitor-less LDO for low-voltage micro-energy-harvested supplies. IEEE Trans. Circuits Syst. I Regul. Pap. 69(2), 599–608 (2022). https://doi.org/10.1109/TCSI.2021.3123057

A. Petrie, Y. Song, W. Kinnison et al., A 0.2-V 10-Bit 5-kHz SAR ADC with dynamic bulk biasing and ultra-low-supply-voltage comparator. IEEE Trans. Circuits Syst. I Regul. Pap. 70(7), 2722–2733 (2023). https://doi.org/10.1109/TCSI.2023.3267067

S. Polineni, M. Bhat, S. Rekha, A switched capacitor-based SAR ADC employing a passive reference charge sharing and charge accumulation technique. Circuits Syst. Signal Process. 39, 5352–5370 (2020). https://doi.org/10.1007/s00034-020-01437-3

E. Rahimi, M. Yavari, Energy-efficient high-accuracy switching method for SAR ADCs. IET Electron. Lett. 50(7), 499–501 (2014). https://doi.org/10.1049/el.2013.3451

S. Rao, K. Reddy, B. Young et al., A deterministic digital background calibration technique for VCO-based ADCs. IEEE J. Solid-State Circuits 49(4), 950–960 (2014). https://doi.org/10.1109/JSSC.2013.2293753

K. Reddy, S. Dey, S. Rao, et al. A 54 mw 12 GS/s 715 dB SNDR 50 MHz BW VCO-based CT ADC using dual phase/frequency feedback in 65 nm CMOS, in Proceedings of the Symposium on VLSI Circuits (VLSI Circuits), pp. C256–C257 (2015). Doi: https://doi.org/10.1109/VLSIC.2015.7231278

A. Sanyal, K. Ragab, L. Chen, et al. A hybrid SAR-VCO ΔΣ ADC with first-order noise shaping, in Proceedings of the IEEE 2014 Custom Integrated Circuits Conference, San Jose, pp. 1–4 (2014). Doi: https://doi.org/10.1109/CICC.2014.6946082

A. Sanyal, N. Sun, An energy-efficient hybrid SAR-VCO ΔΣ capacitance-to-digital converter in 40-nm CMOS. IEEE J. Solid-State Circuits 52(7), 1966–1976 (2017). https://doi.org/10.1109/JSSC.2017.2693237

Y. Shen, X. Tang, X. Xin et al., A 10-bit 100-MS/s SAR ADC with always-on reference ripple cancellation. IEEE Trans. Circuits Syst. I Regul. Pap. 69(10), 3965–3975 (2022). https://doi.org/10.1109/TCSI.2022.3184010

M. Straayer, M. Perrott, A 12-Bit, 10-MHz bandwidth, continuous-time ΣΔ ADC with a 5-Bit, 950-MS/s VCO-based quantizer. IEEE J. Solid-State Circuits 43(4), 805–814 (2008). https://doi.org/10.1109/JSSC.2008.917500

Y. Xie, Y. Liang, M. Liu et al., A 10-Bit 5 MS/s VCO-SAR ADC in 0.18-μm CMOS. IEEE Trans. Circuits Syst. II Express Briefs 66(1), 26–30 (2019). https://doi.org/10.1109/TCSII.2018.2833866

X. Xin, J. Cai, T. Chen et al., A 0.4-V 10-bit 10-KS/s SAR ADC in 0.18 um CMOS for low energy wireless senor network chip. Microelectron. J. 83, 104–106 (2018). https://doi.org/10.1016/j.mejo.2018.11.017

X. Xin, L. Shen, X. Tang et al., A power-efficient 13-Tap FIR filter and an IIR filter embedded in a 10-Bit SAR ADC. IEEE Trans. Circuits Syst. I Regul. Pap. 70(6), 2293–2305 (2023). https://doi.org/10.1109/TCSI.2023.3260085

K. Yoshioka and H. Ishikuro. A 13b SAR ADC with eye-opening VCO based comparator, in ESSCIRC 2014—40th European Solid State Circuits Conference (ESSCIRC), Venice Lido, pp. 411–414 (2014).Doi: https://doi.org/10.1109/ESSCIRC.2014. 6942109

K. Yoshioka, VCO-based comparator: A fully adaptive noise scaling comparator for high-precision and low-power SAR ADCs. IEEE Trans. Very Large Scale Integr. (VLSI) Syst. 29(12), 2143–2152 (2021). https://doi.org/10.1109/TVLSI.2021.3119691

M. Yousefirad, M. Yavari, A fully dynamic third-order EF-CIFF noise-shaping SAR ADC with NTF zeros optimization and passive integration. Int. J. Electron. Commun. 157, 154422 (2022). https://doi.org/10.1016/j.aeue.2022.154422

T. Yousefi, A. Dabbaghian, M. Yavari, An energy-efficient DAC switching method for SAR ADCs. IEEE Trans. Circuits Syst. -II: Express Briefs 65(1), 41–45 (2018). https://doi.org/10.1109/TCSII.2017.2676048

S. Zaliasl, S. Saxena, P. Hanumolu et al., A 12.5-bit 4 MHz 13.8 mW MASH ∆Σ modulator with multirated VCO-based ADC. IEEE Trans. Circuits Syst. I Regul. Pap. 59(8), 1604–1613 (2012). https://doi.org/10.1109/TCSI.2012.2206506

M. Zhang, C. Chan, Y. Zhu et al., A 0.6-V 13-bit 20-MS/s two-step TDC-assisted SAR ADC with PVT tracking and speed-enhanced techniques. IEEE J. Solid-State Circuits 54(12), 3396–3409 (2019). https://doi.org/10.1109/JSSC.2019.2938450

Z. Zhang, M. Cheng, Y. Yu et al., A 0.053 mm2 10-bit 10-ks/s 40-nW SAR ADC with pseudo single ended switching procedure for bio-related applications. Microelectron. J. 139, 105868 (2023). https://doi.org/10.1016/j.mejo.2023.105868

X. Zhou, X. Gui, M. Gusev et al., A 12-bit 20-kS/s 640-nW SAR ADC with a VCDL-based open-loop time-domain comparator. IEEE Trans. Circuits Syst. II Express Briefs 69(2), 359–363 (2022). https://doi.org/10.1109/TCSII.2021.3104215

Z. Zhu, X. Zhou, Y. Du et al., A 14-bit 4-MS/s VCO-based SAR ADC with deep metastability facilitated mismatch calibration. IEEE J. Solid-State Circuits 55(6), 1565–1576 (2020). https://doi.org/10.1109/JSSC.2019.2950188

Acknowledgements

This work is supported in part by the National Natural Science Foundation of China (Nos. 62104193 and 62271389), the Key Scientific Research Program of Shaanxi Provincial Department of Education (No. 22JY058).

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

The authors declare that they have no known competing financial interests or personal relationships that could have appeared to influence the work in this paper.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Xin, X., Zhang, C. & Tong, X. An 11-bit Nyquist SAR-VCO Hybrid ADC with a Reused Ring-VCO for Power Reduction. Circuits Syst Signal Process 43, 1339–1365 (2024). https://doi.org/10.1007/s00034-023-02531-y

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00034-023-02531-y