Abstract

Using of ultra-wideband (UWB) technology in radio transceiver systems has increased in recent years due to high-speed data transmission, low power dissipation, low cost, and low complexity. In particular, distributed amplifier (DA) is a critical component of transceiver in UWB technology. However, designing an ultra-wideband DA with high performance becomes challenging. The DA design suffers from the tight trade-offs between the amplifier parameters such as gain, noise, linearity, input/output impedance matching, and power dissipation. In this paper, a new approach for multi-objective optimization of the DA is introduced. In the proposed approach, the meta-heuristic optimization techniques are applied over the entire bandwidth of the UWB, while the most recent optimization approaches for amplifiers are performed at the center frequency and they can’t achieve the proper design specifications for wideband amplifiers. The simultaneous optimization of power gain (S21), noise figure (NF), input and output return loss (S11 and S22) are conducted over the wide bandwidth using three multi-objective optimization algorithms including Multi-Objective Inclined Planes System Optimization (MOIPO), Non-dominated Sorting Genetic Algorithm II (NSGA-II), and Multi-Objective Particle Swarm Optimization (MOPSO). The obtained results demonstrate the tapered matrix DA optimized by MOIPO exhibits better performance than others. The circuit simulations are performed in 0.18 µm TSMC RF-CMOS technology. Simulation results show that the optimized tapered matrix DA by MOIPO, compared to NSGA-II and MOPSO, exhibits a good performance over the frequency band of 0.1–28 GHz with maximum S21 of 12.9 dB, NF less than 5.9 dB, S11 and S22 below than − 10 dB over the whole frequency band. The DC power dissipation is 25 mW from a 1.5 V supply.

Similar content being viewed by others

Explore related subjects

Discover the latest articles, news and stories from top researchers in related subjects.Data availability

All data generated or analyzed during this study are included in this published paper.

References

Nguyen DP, Nguyen NL, Stameroff AN, Camarchia V, Pirola M, Pham AV (2020) A wideband highly linear distributed amplifier using intermodulation cancellation technique for stacked-HBT cell. IEEE Trans Microw Theory Tech 68(7):2984–2997

Bijari A, Zandian S, Ebrahimipour M (2020) Optimum design of a new ultra-wideband LNA using heuristic multiobjective optimization. J Comput Electron 19:1295–1312

Chien FT, Chan YJ (1999) Bandwidth enhancement of transimpedance amplifier by a capacitive-peaking design. IEEE J Solid-State Circuits 34(8):1167–1170

Chen P, Huang PC, Kuo JJ, Wang H (2011) A 22–31 GHz distributed amplifier based on high-pass transmission lines using 0.18 CMOS µm technology. IEEE Microw Wirel Compon Lett 21(3):160–162

Visweswaran A, Serdijn WA (2009) A low power UWB-LNA using active dual loop negative feedback in CMOS 0.13 µm. In: 2009 IEEE international symposium on circuits and systems, IEEE, pp 225–228

Ghadiri A, Moez K (2011) Compact transformer-based distributed amplifier for UWB systems. IEEE Trans Circuits Syst II Express Briefs 58(5):259–263

Slimane A, Trabelsi M, Moussa MS (2011) Bandwidth improvement technique of distributed amplifiers using combined filtering structures. AEU-Int J Electron Commun 65(10):777–782

Chen KH, Wang CK (2004, August) A 3.1–10.6 GHz CMOS cascaded two-stage distributed amplifier for ultra-wideband application. In: Proceedings of 2004 IEEE Asia-Pacific conference on advanced system integrated circuits, IEEE, p 296–299

Tarar MM, Negra R (2017) Design and implementation of wideband stacked distributed power amplifier in 0.13 µm CMOS using uniform distributed topology. IEEE Trans Microw Theory Tech 65(12):5212–5222

Bhuvaneswari MC (Ed) (2014) Application of evolutionary algorithms for multi-objective optimization in VLSI and embedded systems. Springer

Rocha FA, Martins RM, Lourenço NC, Horta NC (2013) Electronic design automation of analog ICs combining gradient models with multi-objective evolutionary algorithms. Springer Science & Business Media, Berlin

Barros MF, Guilherme JM, Horta NC (2010) Analog circuits and systems optimization based on evolutionary computation techniques, vol 9. Springer, Berlin

Kolakaluri S, Nagura SS, Kar R, Ghoshal SP, Mandal D (2016) Optimization of low noise amplifier using particle swarm optimization. In: 2016 international conference on electrical, electronics, and optimization techniques (ICEEOT), IEEE, p 2055–2058

Papadimitriou A, Bucher M (2017) Multi-objective low-noise amplifier optimization using analytical model and genetic computation. Circuits Syst Signal Process 36(12):4963–4993

Mallick S, Akhil JR, Dasgupta A, Kar R, Mandal D, Ghoshal SP (2017) Optimal design of 5.5 GHz CMOS LNA using hybrid fitness based adaptive de with PSO. In: 2017 international electrical engineering congress (IEECON), IEEE, p 1–4

Joshi D, Dash S, Malhotra A, Sai PV, Das R, Sharma D, Trivedi G (2017) Optimization of 2.4 GHz CMOS low noise amplifier using hybrid particle swarm optimization with Lévy flight. In: 2017 30th international conference on VLSI design and 2017 16th international conference on embedded systems (VLSID), IEEE, p 181–186

Kumar R, Rajan A, Talukdar FA, Dey N, Santhi V, Balas VE (2017) Optimization of 5.5-GHz CMOS LNA parameters using firefly algorithm. Neural Comput Appl 28(12):3765–3779

Bhale VP, Dalal UD (2014) Optimization of CMOS 01.8 µm low noise amplifier using NSGA-II for UWB applications. Int J VLSI Des Commun Syst 5(5):59

Ginzton EL, Jasberg JH, Noe JD, Hewlett WR, Noe JD (1948) Distributed amplification. Proc IRE 36(8):956–969. https://doi.org/10.1109/JRPROC.1948.231624

Niclas KB, Pereira RR (1987) The matrix amplifier: a high-gain module for multioctave frequency bands. IEEE Trans Microw Theory Tech 35(3):296–306

Moez K, Elmasry MI (2008) A low-noise CMOS distributed amplifier for ultra-wide-band applications. IEEE Trans Circuits Syst II Express Briefs 55(2):126–130

Machiels B (2012) Distributed amplification in CMOS. Ph.D disseration, KU Leuven

Piccinni G, Avitabile G, Talarico C, Coviello G (2017) UWB distributed amplifier design using lookup tables and gm over ID methodology. Analog Integr Circ Sig Process 90(3):615–624

Nguyen V, Nam H, Lee B, Park J (2019) A 5.8-17.6 GHz cascaded bi-directional distributed gain amplifier utilizing asymmetric stages in 65 nm CMOS. Microw Opt Technol Lett 61(7):1683–1687

Babaeinik M, Dousti M, Tavakoli MB (2021) Analysis and design of high gain-bandwidth CMOS distributed amplifier utilizing a cascaded pseudo differential distributed amplifier. J Circuits, Syst Comput 30(01):2150005

Alavi SA, Ghadirian S, Chabok SJSM (2017) Bandwidth and gain extension technique for CMOS distributed amplifiers using negative capacitance and resistance cell. Microelectron J 60:60–64

Chiu TY, Wang Y, Wang H (2020) A 3.7–43.7-GHz low-power consumption variable gain distributed amplifier in 90-nm CMOS. IEEE Microw Wirel Compon Lett 31(2):169–172

Nikandish G, Medi A (2017) A 40-GHz bandwidth tapered distributed LNA. IEEE Trans Circuits Syst II Express Briefs 65(11):1614–1618

Machiels B, Reynaert P, Steyaert MS (2012) The tapered matrix amplifier: a low-power high-gain broadband amplifier. Analog Integr Circ Sig Process 73(3):961–972

Zhang Y, Li Z, Li X, Yang H (2019) Efficient design and optimization method for distributed amplifiers. J Shanghai Jiaotong Univ (Sci) 24(3):281–286

Hajimiri A (2020) Distributed integrated circuits: an alternative approach to high-frequency design. IEEE Commun Mag 40(2):168–173

Hodges DA (1999) Darlington’s contributions to transistor circuit design. IEEE Trans Circuits Syst I: Fundam Theory Appl 46(1):102–104

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflict of interest

All authors certify that they have no affiliations with or involvement in any organization or entity with any financial interest or non-financial interest in the subject matter or materials discussed in this manuscript.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Appendices

Appendix 1

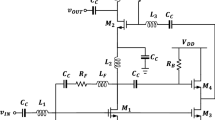

Figure 11 shows the structure of a conventional DA. As shown, the DA consists of two main sections, the gain cells and the gate and drain transmission lines. In CMOS technology, transmission lines are made by the LC network. In addition, the parasitic capacitors of the gain cell transistors (Cgs and Cgd) are usually used as the capacitors required for transmission lines. The input signal is applied to the gate transmission line, and each transistor receives a portion of the input signal and amplifies it through the transmission line. This generates a current at the drain terminal, which is identically divided to the left and right of the drain line. The power of the transistor amplified wave spreads directly in the direction of the load or reverses at any point of the drain line, which causes direct and reverse gain. To achieve a suitable gain, the currents of each transistor must be combined in parallel along the drain line to the amplifier output, meaning that the phase difference between the gate transmission line and the drain must be equal [31].

By selecting the proper propagation constant and the length of the gate and drain transmission lines, the synchronous mode can be achieved. Impedance matching also absorbs waves that are propagating in the opposite direction. Due to the high losses in the gate transmission line, the cut-off frequency of this transmission line is usually lower than the drain line. Therefore, the gate transmission line capacitors (Cg) and its inductors (Lg) limit the cut-off frequency of DAs [32]. The gain of a conventional distributed amplifier is given as follows:

where n and Gm are the number of stages and the transconductance of each stage, respectively, RL is the load of the transmission line. To attain the maximum available power gain, it is essential that the characteristic impedance and the cut-off frequency of the gate transmission lines be equal. The cut-off frequency and characteristic impedance of gate and drain transmission lines are given as follows:

According to (6), the gain of the amplifier is determined by the total transconductance and the number of parallel transistors. Also, the bandwidth of the amplifier is only limited by the cut-off frequency of parallel transistors. However, essentially, half of the output power is dissipated by the reverse currents that flew through one of the terminating resistors of the output transmission line. Therefore, with regards to the low power performance of DAs, their power consumption is fairly high. Moreover, adding any active and passive components leads to higher power dissipation and overall noise figure, as well. So far, various methodologies have been proposed to overcome these problems to some extent. Ginzton et al. [19] proposed a new DA by tapering the output transmission line, as shown in Fig. 12. According to (8), the smaller capacitance should be provided for higher value of the characteristic impedance at the output transmission line. Therefore, the size of the parallel transistors is reduced. Therefore, the tapered output transmission line limits the gain of the DA. Furthermore, the output impedance matching of the tapered DA is highly frequency-dependent as the terminating resistor on the left of the output transmission line has been removed.

Schematic of DA with tapered output transmission line [19]

The matrix DA structure has been proposed to use multiplicative and additive gain mechanisms simultaneously [20]. The basic schematic of the matrix DA is illustrated in Fig. 13. Ideally, due to the reverse currents of interstage transmission line amplification, the matrix DAs exhibit higher gain than cascaded amplifiers. However, the power consumption of the matrix DA is relativity high due to terminating resistors at the output and interstage transmission lines. Moreover, the gain of the matrix DA is highly frequency-dependent because of multiple reverse amplification paths, which introduce different delays.

As illustrated in Fig. 14, using the new technique proposed in [22] for tapered DA, the coefficients of the gain cell’s current and characteristic impedance of the first section are a0 = b0 = 1.

The current coefficient of the gain cell and the characteristic impedance of the kth section is also given respectively as follows [22]:

where S denotes the sum of the current coefficients and is obtained as follows:

where N presents the number of parallel gain cells in the DA. In this design, S is assumed to be equal to 3. It should be noted Eq. (10) cannot be satisfied for the leftmost section (k = N−1), and the value for aN−1 is given by [22]:

Appendix 2

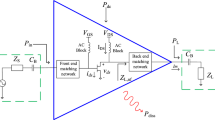

Today, the modern signal processing systems utilize a combination of analog and digital techniques, and are implemented on a chip, have three main goals of short design time, increasing productivity, and reducing circuit complexity. The semiconductor component manufacturing technologies have reached nanometer dimensions and are growing exponentially, but the computer-aided design (CAD) tools of analog circuits are not grown in this proportion. All kinds of meta-heuristic optimization algorithms seem to be suitable tools for analog RF circuit optimization. The purpose of optimization is to find the best acceptable solutions, given the constraints and needs of the problem. For a problem, there may be different solutions that are defined for comparing them and selecting the optimal solution called the objective function. For example, direct power gain (S21), noise figure (NF) and input return loss (S11), and output return loss (S22) are the common objectives of the optimizing DA circuits. Sometimes simultaneous optimization is considered. Such optimization problems, which include multiple objective functions, are called multi-objective problems. In multi-objective optimization, the goal is to solve problems such as [15]:

Subject to:

where x = [x1, x2,...,xn]T is the vector of decision variables, fi: Rn → R, i = 1,...,m are the objective functions and gi, hj: Rn → R, i = 1,..., p, j = 1,..., q are the constraint functions of the problem. The target is to achieve a solution that works for (15) and (16).

Figure 15 shows the relationship between the MATLAB environment and the circuit simulator software. It should be noted the circuit simulation is carried out by Advanced Design System (ADS) with 180-nm RF-TSMC CMOS technology. First, the input information, including the size of the design parameters, is specified by MATLAB. Then, ADS is executed, and finally, the objective functions for processing are read.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Bijari, A., Zandian, S., Soruri, M. et al. A new approach to multi-objective optimization of a tapered matrix distributed amplifier for UWB applications. Neural Comput & Applic 36, 1833–1847 (2024). https://doi.org/10.1007/s00521-023-09167-8

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s00521-023-09167-8