Abstract

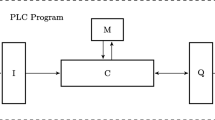

This paper presents a formal framework for verifying distributed embedded systems. An embedded system is described as a set of concurrent real time functions which communicate through a network of interconnected switches involving messages queues and routing services.In order to allow requirements verification, such a model is then translated into timed automata. However, the complexity inherent in distributed embedded systems often does not allow to apply model checking techniques. Consequently, the paper presents an abstraction-based verification method which consists in abstracting the communication network by end-to-end timed channels. To prove a given safety property φ requires then (1) to prove a set of proof obligations ensuring the correctness of the abstraction step (i.e. the end-to-end channels correctly abstract the network), and (2) to prove φ at the abstract level. The expected advantage of such a method lies in the ability to overcome the combinatorial explosion frequently met when verifying complex systems. This method is illustrated by an avionic case study.

Similar content being viewed by others

References

Aceto, L., Bouyer, P., Burgueño, A., Larsen, K.G.: The power of reachability testing for timed automata. In: Proceedings of the 18th Conference Foundation of Software Technology and Theoretical Computer Science (FST & TCS’98), Chennai, India, December 1998, vol. 1530, pp. 245–256. Springer, Berlin Heidelberg New York (1998)

Aceto L., Burgueño A., Larsen K.G. (1998) Model checking via reachability testing for timed automata. In: Steffen B. (eds). TACAS’98, LNCS 1384. Springer, Berlin Heidelberg New York, pp. 263–280

Alur R., Courcoubetis C., Dill D.L. (1993) Model-checking in dense real-time. Inf. Comput. 104(1): 2–34

Alur R., Dill D.L. (1994) A theory of timed automata. Theor. Comput. Sci. 126(2): 183–235

Bozga M., Daws C., Maler O., Olivero A., Tripakis S., Yovine S. (1998) Kronos: a model-checking tool for real-time systems. In: Hu A.J., Vardi M.Y. (eds). Proceedings of the 10th International Conference on Computer Aided Verification, Vancouver, Canada, vol. 1427. Springer, Berlin Heidelberg New York, pp 546–550

Burgueño-Arjona, A.: Verification and Synthesis of Timed Systems using Parametric Analysis and Observation Methods. PhD thesis, Ecole Nationale Supérieure de l’aéronautique et de l’espace (1998)

Cruz R.L. (1991) Calculus for network delay-part. I: Network elements in isolation. IEEE Trans. Inform. Theor. 37(1): 114–131

Havelund, K., Skou, A., Larsen, K.G., Lund, K.: Formal modeling and analysis of an audio/video protocol: an industrial case study using uppaal. In: Proceedings of the 18th IEEE Real-Time Systems Symposium (RTSS ’97). IEEE Computer Society (1997)

Henzinger T.A., Ho P.-H., Wong-Toi H. (1997) HYTECH: a model checker for hybrid systems. Int. J. Softw. Tools Technol. Transfer 1(1–2): 110–122

Jain R. (1991) The Art of Computer Systems Performance Analysis - techniques for Experimental Design, Measurement, Simulation and Modeling. Wiley, New York

Kleinrock L. (1975) Queueing systems—volume 1: theory. Wiley, New york

Laroussinie, F., Larsen, K.G.: CMC: A tool for compositional model-checking of real-time systems. In: Proceedings of the IFIP Joint International Conference Formal Description Techniques & Protocol Specification, Testing, and Verification (FORTE-PSTV’98), Paris, France, Nov. 1998, pp. 439–456. Kluwer, Dordrecht (1998)

Larsen K.G., Pettersson P., Yi W. (1997) UPPAAL in a nutshell. Int. J. Softw. Tools Technol. Transfer, 1(1–2): 134–152

Le Boudec, J.Y. Thirian, P.: Network Calculus—a theory for Deterministic Queueing Systems for the Internet, vol. LNCS 2050. Springer Berlin Heidelberg New York.

Schnoebelen P. et al. (2001) Systems and Software Verification Model-Checking Techniques and Tools. Springer, Berlin Heidelberg Newyork

Starobinski, D., Karpovsky, M., Zakrevski, L.: Application of network calculus to general topologies using turn-prohibition (2002)

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Carcenac, F., Boniol, F. A formal framework for verifying distributed embedded systems based on abstraction methods. Int J Softw Tools Technol Transfer 8, 471–484 (2006). https://doi.org/10.1007/s10009-006-0011-0

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10009-006-0011-0