Abstract

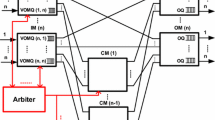

Buffered Clos-network switches have advantages of modularity and simplicity; however, they are limited to serious out-of-sequence problems, especially when serving multicast traffic. In this study, a frame-based multicast scheduling algorithm for memory-memory-memory Clos networks (FMClos) is proposed. Multicast cells are replicated at the first and last stages based on address-copy technology, which eliminates head-of-line (HoL) blocking and improves throughput performance. The frame-based scheduling scheme performed at the input module, as well as the buffered crossbar switch element adopted by the central module, contributes to reducing the out-of-sequence (OOS) cells. Simulation results show that FMClos scheme can achieve nearly 100% throughput. In comparison with existing algorithms, the proposed method decreases the proportion of OOS cells and considerably reduces resequencing delay under heavy traffic load.

Similar content being viewed by others

References

Qiu, T., Zhang, Y.S., Qiao, D.J., et al.: A robust time synchronization scheme for industrial Internet of things. IEEE Trans. Ind. Inf. PP(99), 1–11 (2017)

Maragatham, S., Davina, V., Sangaiah, A.K.: Teaching and learning in the social networking sites era. Asia-Pac. Stud. 1(1), 68–75 (2014)

Miao, Y.B., Ma, J.F., Jiang, Q. et al.: Verifiable keyword search over encrypted cloud data in smart city. Comput. Electr. Eng. (2017). https://doi.org/10.1016/j.compeleceng.2017.06.021

Sun, S.T., He, S.M., Zheng, Y.F. et al.: Multicast scheduling in buffered crossbar switches with multiple input queues. In: Proceedings of the 2005 IEEE HPSR, pp. 73–77

Mhamdi, L.: On the integration of unicast and multicast cell schedulingin buffered crossbar switches. IEEE Trans. Parallel Distrib. Syst. 20(6), 818–830 (2009)

McKeown, N., Prabhakar, B.: Scheduling multicast cells in an input-queued switch. In: Proceedings of the 1996 IEEE INFOCOM, pp. 271–278

Pan, D., Yang, Y.Y.: FIFO-based multicast scheduling algorithm for virtual output queued packet switches. IEEE Trans. Comput. 54(10), 1283–1297 (2005)

Dong, Z.Q., Rojas-Cessa, R.: Input- and output-based shared-memory crosspoint-buffered packet switches for multicast traffic switching and replication. In: Proceedings of the 2008 IEEE ICC, pp. 5659–5663

Yan, F.L., Xiong, Q.X., Xiao, H., et al.: Achieving 100% throughput for integrated uni- and multicast traffic without speedup. Int. J. Commun. Netw. Syst. Sci. 10, 35–42 (2017)

Singh, A., Ong, J., Agarwal, A., et al.: Jupiter rising: a decade of Clos topologies and centralized control in Google’s datacenter network. In: Proceedings of the 2015 ACM SIGCOMM, pp. 183–197

Yang, Y., Wang, J.: Wide-sense nonblocking Clos-networks under packing strategy. IEEE Trans. Comput. 48(3), 265–284 (1999)

Oki, E., Jing, Z., Rojas-Cessa, R., et al.: Concurrent round-robin-based dispatching schemes for Clos-network switches. IEEE/ACM Trans. Netw. 10(6), 830–844 (2002)

Liu, K., Yan, J., Gao, X.L., et al.: Fully distributed fault tolerant scheduling for onboard Clos-network switching. J. Electron. Inf. Technol. 38(6), 1377–1384 (2016)

Alfaraj, N., Xu, Y., Chao, H.J.: A practical and scalable congestion control scheme for high-performance multi-stage buffered switches. In: Proceedings of the 2012 IEEE HPSR, pp. 44–51

Xia, Y., Hamdi, M., Chao, H.J.: A practical large-capacity three-stage buffered Clos-network switch architecture. IEEE Trans. Parallel Distrib. Syst. 27(2), 371-328 (2016)

Yang, J.G., Bao, M.Q., Liu, Z.J., et al.: A distributed scheduling algorithm maintaining cells order for three-stage Clos networks. Chin. J. Comput. 31(3), 467–475 (2008)

Kang, M., Kyung, C.: Three-stage Clos-network switch architecture with buffered center stage for multi-class traffic. J. Circuit Syst. Comput. 5(2), 263–276 (2006)

Dong, Z.Q., Rojas-Cessa, R., Oki, E.: “Memory-memory-memory Clos network packet switches with in-sequence service. In: Proceedings of the 2011 IEEE HPSR, pp. 121–125

Dong, Z.Q., Rojas-Cessa, R.: MCS: buffered Clos-network switch with in-sequence packet forwarding. In: Proceedings of the 2012 IEEE SARNOFF, pp. 1–6

Gao, Y., Qiu, Z.L., Zhang, J.: Providing 100% throughput in buffered Clos-network switches with in-sequence service. IET Commun. 8(1), 133–139 (2014)

Li, X., Zhou, Z., Hamdi, M.: Space-memory-memory architecture for Clos-network packet switches. In: Proceedings of the 2005 IEEE ICC, pp. 1031–1035

Hao, Y., Ruepp, S., Berge, M.S.: Out-of-sequence preventative cell dispatching for multicast input-queued space-memory-memory Clos-network. In: Proceedings of the 2011 IEEE HPSR, pp. 230–235

She, Y., Panwar, S., Chao, H.J.: Design and performance analysis of a practical load-balanced switch. IEEE Trans. Commun. 57(8), 2420–2429 (2009)

Jaramillo, J., Milan, F., Srikant, R.: Padded frames: a novel algorithm for stable scheduling in load-balanced switches. IEEE/ACM Trans. Netw. 16(5), 1212–1225 (2008)

Yu, H.: A novel round-robin based multicast scheduling algorithm for 100 Gigabit Ethernet switches. In: Proceedings of the 2010 IEEE INFOCOM, pp. 1–2

Acknowledgements

This work is partially supported by the National Natural Science Foundation of China (Grant No. 61502204), the Qing Lan Project of Jiangsu and the Science and Technology Innovation Team of Wuxi Institute of Technology (Grant No. 3115008931).

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Gao, Y., Xiao, Y. Frame based multicast scheduling for buffered Clos-network switches. Cluster Comput 22 (Suppl 2), 2563–2570 (2019). https://doi.org/10.1007/s10586-017-1328-z

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10586-017-1328-z