Abstract

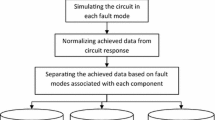

A new neural network-based analog fault diagnosis strategy is introduced. Ensemble of neural networks is constructed and trained for efficient and accurate fault classification of the circuit under test (CUT). In the testing phase, the outputs of the individual ensemble members are combined to isolate the actual CUT fault. Prominent techniques for producing the ensemble are utilized, analyzed and compared. The created ensemble exhibit high classification accuracy even if the CUT has overlapping fault classes which cannot be isolated using a unitary neural network. Each neural classifier of the ensemble focuses on a particular region in the CUT measurement space. As a result, significantly better generalization performance is achieved by the ensemble as compared to any of its individual neural nets. Moreover, the selection of the proper architecture of the neural classifiers is simplified. Experimental results demonstrate the superior performance of the developed approach.

Similar content being viewed by others

References

M. A. El-Gamal, “A Knowledge-Based Approach for Fault Detection and Isolation in Analog Circuits,” Proc. IEEE Int. Conference on Neural Networks, Houston, Texas, vol. 3, pp. 1580–1584, 1997.

M. A. El-Gamal and M. Abu El-Yazeed, “A Combined Clustering and Neural Network Approach for Analog Multiple Hard Fault Classification,” J. Electron. Test: Theory and Appl., (Kluwer) vol. 14, pp. 207–217, 1999.

M. A. El-Gamal, “Genetically Evolved Neural Networks for Fault Classification in Analog Circuits,” Neural Comput. Appl., (Springer), vol. 11, pp. 112–121, 2002.

M. A. El-Gamal and M. Abdulghafour, “Fault Isolation in Analog Circuits using a Fuzzy Inference System,” Computers and Electrical Engineering, (Pergamon), vol. 29, pp. 213–229, 2003.

R. Spina and S. Upadhyaya, “Linear Circuit Fault Diagnosis using Neuromorphic Analyzers,” IEEE Trans. Circuits Syst. 2, vol. 44, pp. 188–196, 1997.

M. Catelani and A. Fort, “Fault Diagnosis of Electronic Circuits using a Radial Basis Function Network Classifier,” Measurements, vol. 28, pp. 147–154, 2000.

F. Aminian, M. Aminian and H. Collins, “Analog Fault Diagnosis of Actual Circuits using Neural Networks,” IEEE Trans. Instrum. Meas., vol. 51, pp. 544–550, 2002.

A. J. C. Sharkey (ed.), “Combining Artificial Neural Nets,” Berlin Heidelberg New York: Springer, 1999.

L. Breiman, “Combining predictors,” in Combining Artificial Neural Nets, A. J. C. Sharkey (ed.), Berlin Heidelberg New York: Springer, 1999.

S. Haykin, “Neural Networks: A Comprehensive Foundation,” Second Edition, Englewood Cliffs, NJ: Prentice Hall, 1999.

D. Opitz and R. Maclin, “Popular Ensemble Methods: An Empirical Study,” J. Artif. Intell. Res., vol. 11, pp. 169–198, 1999.

V. Tresp, “Committee Machines,” Handbook for Neural Network Signal Processing, Yu Hen Hu and Jenq-Neng Hwang (eds.), Boca Raton, FL: CRC, 2001.

Y. Freund and R. E. Schapire, “A Short Introduction to Boosting,” J. Japan. Soc. Artif. Intell., vol. 14, pp. 771–780, 1999. (In Japanese, translation by Naoki Abe.)

E. Bauer and R. Kohavi, “An Empirical Comparison of Voting Classification Algorithms: Bagging, Boosting, and Variants,” Mach. Learn., vol. 36, pp. 105–139, 1999.

S. Geman, E. Bienenstock, and R. Doursat, “Neural Networks and the Bias/Variance Dilemma,” Neural Comput., vol. 4, pp. 1–58, 1992.

J. A. Starzyk and M. A. El-Gamal, “Artificial Neural Network for Testing Analog Circuits,” Proc IEEE Int Symp Circuit and Systems, New Orleans, LA, vol. 3, pp. 1851–1854, 1990.

G. Rutkowski, “A Neural Approach to Fault Location in Nonlinear DC Circuits,” Proc Int Conf on Artificial Neural Networks, Brighton, pp. 1123–1126, 1992.

A. Fanni, A. Giua and E. Sandoli, “Neural Networks for Multiple Fault Diagnosis in Analog Circuits,” Neural Networks Theory, Technology and Applications, IEEE Technology Update series, pp. 745–752, 1996.

C. Patern, R. Saeks, and R. Pap, “Fault Diagnosis and Neural Networks,” Proc. IEEE Int. Conf. Syst. Man Cybern., (Charlottesville), VA, pp. 1517–1521, 1991.

M. A. El-Gamal and A. Z. Ghalwash, “A Neuro-Expert System Architecture for Analog Fault Diagnosis,” Proc Int ICSC Symp on Engineering of Intelligent Systems, Tenerife, Spain, vol. 2, pp. 227–233, 1998.

S. Yu, B. Jervis, K. Eckersall, I. Bell, A. Hall and G. Taylor, “Neural Network Approach to Fault Diagnosis in CMOS Opamps with Gate Oxide Short Faults,” Electronic Letters, vol. 30, pp. 695–696, 1994.

Y. Maidon, B. Jervis, N. Dutton, and S. Lesage, “Diagnosis of Multifaults in Analog Circuits Using Multilayer Perceptrons,” IEE Proc., Circ. Devices Syst., vol. 144, pp. 149–154, 1997.

R. Duda, P. Hart, and D. Stork, “Pattern Classification,” second edition, New York: Wiley, 2001.

V. Prasad and N. Babu, “On Minimal Set of Test Nodes for Fault Dictionary of Analog Circuit Fault Diagnosis,” J. Electron. Test: Theory Appl., (Kluwer), vol. 7, pp. 255–258, 1995.

E. Bauer and R. Kohavi, “An Empirical Comparison of Voting Classification Algorithms: Bagging, Boosting, and Variants,” Machine Learning, Kluwer Academic publishers,vol. 36, pp. 105–139, 1999.

Pspice Circuit Analysis User’s Guide, The MicroSim Corp., CA, USA, 1992.

M. Aminian and F. Aminian, “Neural-Network Based Analog-Circuit Fault Diagnosis Using Wavelet Transform as Preprocessor,” IEEE Trans. Circuits Syst., 2, vol. 47, pp. 151–156, 2000.

B. Cannas, A. Fanni, S. Manetti, A. Montisci, and M. C. Piccirilli, “Neural Network-Based Analog Fault Diagnosis Using Testability Analysis,” Neural Comput. Appl., (Springer), vol. 13, pp. 288–298, 2004.

Author information

Authors and Affiliations

Corresponding author

Additional information

Editor: B. Kaminska

Rights and permissions

About this article

Cite this article

El-Gamal, M.A., Mohamed, M.D.A. Ensembles of Neural Networks for Fault Diagnosis in Analog Circuits. J Electron Test 23, 323–339 (2007). https://doi.org/10.1007/s10836-006-0710-1

Received:

Revised:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-006-0710-1