Abstract

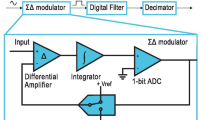

Evaluating the digital stimuli used in the design-for-digital-testability (DfDT) Σ-Δ modulator is a time-consuming task due to its oversampling and non-linear nature. Although behavioral simulations can substantially improve the simulation speed, conventional behavioral models fail to provide accurate enough signal-to-noise ratio (SNR) predictions for this particular application. In this paper, a fully-settled linear behavior plus noise (FSLB+N) model for the DfDT Σ-Δ modulator is presented to improve both the accuracy and the speed of the behavioral simulations. The model includes the following parameters: the finite open-loop gains, the offsets, the finite output swings, the flicker noise of the operational amplifiers (OPAMPs), as well as the thermal noises of the switched capacitors, the OPAMPs, and the reference supplies. With the proposed model, the behavioral simulation results demonstrate a high correlation with the measurement data. On average, the SNR difference between the simulation and the measurement is –1.1 dB with a maximum of 0.05 dB and a minimum of –2.2 dB. Comparing with the circuit-level simulation using HSPICE, the behavioral simulation with the FSLB+N model is 1,190,000 times faster. The proposed model not only can be used for evaluating the digital stimulus candidates, but also can be applied to system-level simulations of the mixed-signal design with an embedded DfDT Σ-Δ modulator.

Similar content being viewed by others

References

Burns M, Roberts GW (2001) An introduction to mixed-signal IC test and measurement. Oxford University Press, Oxford

Haurie X, Roberts GW (1998) Arbitary-precision signal generation for mixed-signal built-in self-test. IEEE Trans Circuits Syst 2 Analog Digit Signal Process 45(11):1425–1432

Hong H-C (2004) Design-for-digital-testability 30 MHz second-order Sigma-Delta modulator. In: Procedings of the IEEE custom integrated circuits conference (CICC). IEEE Computer Society, Washington, DC, pp 211–214

Hong H-C, Huang J-L, Cheng K-T, Wu C-W, Kwai D-M (2003) Practical considerations in applying Sigma-Delta modulation-based analog BIST to sampled-data systems. IEEE Trans Circuits Syst 2 Analog Digit Signal Process 50(9):553–566

Hong H-C, Liang S-C (2006) A cost effective output response analyzer for Sigma-Delta modulation based BIST systems. In: IEEE Asian Test Symposium (ATS), Software Research Park, Fukuoka, 20–23 November 2006, pp 255–261

Hong H-C, Wu C-W (2004) Selection of the high-order analog response extractor for Sigma-Delta modulation based analog built-in self-test applications. Int J Electr Eng Educ 11(2):103–115

Kuo T-H, Chen K-D, Chen J-R (1999) Automatic coefficients design for high-order Sigma-Delta modulators, IEEE Trans Circuits Syst 2 Analog Digit Signal Process 46(1):6–15

Loukusa V (2002) Behavioral test generation modeling approach for mixed-signal IC verification. In: International mixed-signals testing workshop (IMSTW), Montreux, 2002

Malcovati P, Brigati S, Francesconi F, Maloberti F, Cusinato P, Baschirotto A (2003) Behavioral modeling of switched-capacitor Sigma-Delta modulators. IEEE Trans Circuits Syst 1 Fundam Theory Appl 50(3):352–364

Norsworthy SR, Schreier R, Temes GC (1997) Delta-Sigma data converters: theory, design, and simulation. IEEE Press, Piscataway

Oppenheim AV, Schafer RW (1989) Discrete-time signal processing. Prentice-Hall, Englewoods Cliffs

Razavi B (2001) Design of analog CMOS integrated circuits. McGraw-Hill, New York

Roy A, Sunter S, Fudoli A, Appello D (2002) High accuracy stimulus generation for A/D converter BIST. In: Proceedings of the international test conference (ITC). IEEE Computer Society, Washington, DC, pp 1031–1039

Toner MF, Roberts GW (1995) A BIST scheme for a SNR, gain tracking, and frequency response test of a Sigma-Delta ADC. IEEE Trans Circuits Syst 2 Analog Digit Signal Process 42(1):1–15

Venuto DD, Dell’Olio F, Reyneri L (2005) Optimization of FPGA-based test strategy for high resolution ADC. In: International mixed-signals testing workshop (IMSTW), Cannes, 27–29 June 2005, pp 250–259

Acknowledgments

This work is supported by National Science Council, Taiwan R.O.C. under Grant NSC93-2215-E009-050. The author would also like to thank Dr. Hsien-Hsin S. Lee of Georgia Tech for his comments on this work.

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: M. Lubaszewski

Rights and permissions

About this article

Cite this article

Hong, HC. A Fully-Settled Linear Behavior Plus Noise Model for Evaluating the Digital Stimuli of the Design-for-Digital-Testability Σ-Δ Modulators. J Electron Test 23, 527–538 (2007). https://doi.org/10.1007/s10836-007-5005-7

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-007-5005-7