Abstract

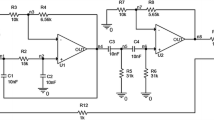

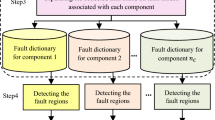

Most of the recently reported test point selection algorithms for analog fault dictionary techniques are based on integer-coded table (ICT) technique. Hence, the accuracy of these algorithms is closely related to the accuracy of the ICT technique. Unfortunately, this technique is not accurate, especially when the size of fault dictionary is large. This paper proposes an accurate fault-pair Boolean table technique for the test point selection problem. First, the approach to transform the fault dictionary into a fault-pair Boolean table is introduced. Then, a test point selection algorithm based on the fault-pair Boolean table is proposed. Thirdly, several example circuits are used to illustrate the proposed algorithm. Simulated results indicate that the proposed method is more accurate than the other methods. Therefore, it is a good solution for minimizing the size of the test point set.

Similar content being viewed by others

References

Abderrahman, Cerny E, Kaminska B (1996) Optimization-based multifrequency test generation for analog circuits. J Electron Test Theory Application 9:59–73

Augusto JS, Almeida C (2006) A tool for test point selection and single fault diagnosis in linear analog circuits. In Proc. XXI Intl. Conf. On Design of Systems and Integrated Systems DCIS’06, Barcelona, Spain

Bandler JW, Salama AE (1985) Fault diagnosis of analog circuits. Proc IEEE 73:1279–1325

Golonek T, Rutkowski J (2007) Genetic-Algorithm-Based Method for Optimal analog test points selection. IEEE Trans Circuits Syst II, Exp Briefs 54(2):117–121

Hochwald W, Bastian JD (1979) A dc approach for analog fault dictionary determination. IEEE Trans Circuits Syst CAS-26:523–529

Lin PM, Elcherif YS (1985) Analogue circuits fault dictionary—New approaches and implementation. Inl J Circuit Theory Appl 13:149–172

Peng W, Shiyuan Y (2006) A soft fault dictionary method for analog circuit diagnosis based on slope fault mode. Control Autom 22(6):1–23

Pinjala KK, Kim BC (2003) An Approach for Selection of Test nodes for Analog Fault diagnosis. Proceedings of the 18th IEEE International Symposium on Defect and Fault Tolerance in VLSI Systems

Prasad VC, Babu NSC (2000) Selection of test nodes for analog fault diagnosis in dictionary approach. IEEE Trans Instrum Meas 49:1289–1297

Prasad VC, Rao Pinjala SN (1995) Fast algorithms for selection of test nodes of an analog circuit using a generalized fault dictionary approach. Circ Syst Signal Process 14(6):707–724

Spaandonk J, Kevenaar T (1996) Iterative test-point selection for analog circuits. In Proc 14th VLSI Test Symp 66–71

Starzyk JA, Liu D, Liu Z-H, Nelson DE, Rutkowski JO (2004) Entropy-based optimum test nodes selection for analog fault dictionary techniques. IEEE Trans Instrum Meas 53:754–761

Stenbakken GN, Souders TM (1987) Test point selection and testability measure via QR factorization of linear models. IEEE Trans Instrum Meas IM-36(6):406–410

Varaprasad KSVL, Patnaik LM, Jamadagni HS, Agrawal VK (2007) A new ATPG technique (ExpoTan) for testiong analog circuits. IEEE Trans Computer-Aided Design 26(1):189–196

Varghese X, Williams JH, Towill DR (1978) Computer-aided feature selection for enhanced analog system fault location. Pattern Recognit 10:265–280

Yang C, Tian S, Binglong (2009) Test point selection for analog fault dictionary techniques. J Electron Test Theory Application 25(2):157–168

Yang CL, Tian SL, Long B (2009) Application of heuristic graph search to test point selection for analog fault dictionary techniques. IEEE Trans Instrum Meas 58(7):2145–2158

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: J. W. Sheppard

Rights and permissions

About this article

Cite this article

Yang, C., Tian, S., Long, B. et al. A Novel Test Point Selection Method for Analog Fault Dictionary Techniques. J Electron Test 26, 523–534 (2010). https://doi.org/10.1007/s10836-010-5169-4

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-010-5169-4