Abstract

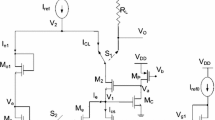

In this paper, a current-mode Built-In Self-Test (BIST) scheme is proposed for on-chip estimating static non-linearity errors in current-steering digital-to-analog converters (DACs). The proposed DAC BIST scheme is designed to verify a 10-bit segmented current-steering DAC, consist of a 5-bit coarse DAC and a 5-bit fine one. This proposed BIST scheme includes a current-mode sample-and-difference circuit to increase the sampling current accuracy and control a current-controlled oscillator (ICO). In addition, only 36 measurements are required by using the selected-code method rather than 1024 measurements for the conventionally-utilized all-code method. Compared to the conventionally-utilized all-code method, about 85-% reduction of test time can be achieved.

Similar content being viewed by others

References

Arabi K, Kaminska B (1998) On chip testing data converters using static parameters. IEEE Trans Very Large Scale Integr (VLSI) Syst 6(3):409–419

Arabi K, Kaminska B, Rzeszut J (1994) A built-in-self-test approach for medium to high-resolution digital-to-analog converters. In: Proc IEEE Asian Test Symp(ATS), pp 373–378

Burns M, Roberts GW (2001) An introduction to mixed-signal IC test and measurement. Oxford University Press, Oxford

Chang S-J, Lee C-L, Chen J-E (2002) BIST scheme for DAC testing. Electron Lett 38(7):776–777

Daubert SJ, Vallancourt D (1990) Operation and analysis of current copier circuit. IEE Proceeding 137(4):109–115

Daubert SJ, Vallancourt D, Tsividis YP (1988) Current copier cells. Electron Lett 24(12):1560–1562

Fiez TS, Liang G, Allstot DJ (1991) Switch-current circuit design issues. IEEE J Solid-State Circuits (JSSC) 26(3):192–202

Hassan I HS, Arabi K, Kaminska B (1998) Testing digital to analog converters based on oscillation test strategy using sigma-delta modulation. In: Proc Int Conf Comput Des, pp 40-46

Huang J-L, Ong C-K, Cheng K-T (2000) A BIST scheme for on-chip ADC and DAC testing. In: Proc Design Automat Conf (DAC) pp 216–220

Johns D, Martin K (1997) Analog integrated circuit design. Wiley, New York

Kester W (2005) The data conversion handbook. Analog Devices

Lakshmikumar KR, Hadaway RA, Copland MA (1986) Characterization and modeling of mismatch in MOS transistor for precision analog design. IEEE J Solid-State Circuits (JSSC) 21(12):1057–1066

Pelgrom M, Duinmaijer A, Welbers A (1989) Matching properties of MOS transistors. IEEE J Solid-State Circuits (JSSC) 24(10):1433–1439

Rafeeque KPS, Vasudevan V (2004) A built-in-self-test scheme for digital to analog converters. In: Proc Int Conf Very Large Scale Integr Des, pp 1027–1032

Rafeeque KPS, Vasudevan V (2004) A built-in-self-test scheme for segmented and binary weighted DACs. J Electron Test Theory Appl (JETTA) 20(12):623–638

Toumazou C, Hughes JB, Pattullo DM (1990) A regulated cascode switching-current memory cell. Electron Lett 26(3):303–304

Vallancourt D, Tsividis YP, Daubert SJ (1989) Sample-current circuits. In: Proc IEEE Int Symp Circuits and Systs (ISCAS) pp 1592–1595

Van den Bosch A, Steyaert M, Sansen W (2000) An accurate statistical yield model for CMOS current-steering D/A converters. In: Proc IEEE Int Symp Circuits and Systs (ISCAS) pp 105–108

Van den Bosch A, Steyaert M, Sansen W (2004) Static and dynamic performance limitations for high speed D/A converters. Kluwer Academic, Boston

Wegmann G, Vittoz EA (1990) Analysis and improvements of accurate dynamic current mirrors. IEEE J Solid-State Circuits (JSSC) 25(6):699–706

Wen Y-C, Lee K-J (1998) BIST structure for DAC testing. Electron Lett 34(12):1173–1174

Acknowledgment

This work was supported in part by the grant of NSC-98-2218-E-151-006 from National Science Council (NSC), Taiwan.

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: M. Margala.

Rights and permissions

About this article

Cite this article

Ting, HW., Chang, SJ. & Huang, SL. A Design of Linearity Built-in Self-Test for Current-Steering DAC. J Electron Test 27, 85–94 (2011). https://doi.org/10.1007/s10836-010-5187-2

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-010-5187-2