Abstract

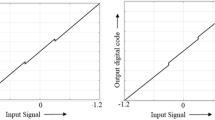

This paper presents a design-for-diagnosis method to identify error sources in pipelined analog-to-digital converters (ADCs). In the proposed method, the stage under test (SUT) is configured to separate each error effect contained in its output residual signal. Two stages after the SUT are configured as a cyclic ADC to digitize the residual output voltage of the SUT. Critical circuit parameters, namely, op-amp gain, capacitor mismatch, op-amp offset, and comparator offset, are identified in the digital domain. Accurate analog test input signals are not necessary for the proposed design-for-diagnosis scheme. A simple digital decoder is employed to generate test control signals. Several additional switches are used to perform SUT re-configuration, which induce minor area overhead. Behavioral and circuit simulations are performed to show the effectiveness of the proposed method.

Similar content being viewed by others

References

Charoenrook A, Soma M (1993) Fault diagnosis of flash ADC using DNL test. in Proc. IEEE International Test Conference. Oct. 680–689

Charoenrook A, Soma M (1994) Fault diagnosis technique for subranging ADCs. in Proc. IEEE International Test Conference. Nov. 367–372

Chiu Y, Gray PR, Nikolic B (2004) A 14-b 12-MS/s CMOS pipeline ADC with over 100-dB SFDR. IEEE J Solid-State Circuits 39(3):2139–2151

Cho TB, Gray PR (1995) A 10 b 20 Msample/s, 35 mW pipeline A/D converter. IEEE J Solid-State Circuits 30:166–172

Cusinato P, Bruccoleri M, Caviglia DD, Valle M (1998) Analysis of the behavior of a dynamic latch comparator. IEEE Trans Circuits Syst I, Fundam Theory Appl 45(3):294–298

Huang CH, Lee KJ, Chang SJ (2004) A low-cost diagnosis methodology for pipelined A/D converters. in Proc. IEEE Asian Test Symposium. Nov. 296–301

Kuyel T, Bilhanhen H (1999) Relating linearity test results to design flaws of pipelined analog to digital converters. in Proc. IEEE International Test Conference. Sept. 772–779

Lewis SH, Gray PR (1987) A pipelined 5-Msample/s 9-bit analog-to-digital converter. IEEE J Solid-State Circuits 22:954–961

Lin JF, Chang SJ, Huang CH (2009) Design-for-test circuit for the reduced code based linearity test method in pipelined ADCs with digital error correction technique. in Proc. IEEE Asian Test Symposium. Nov. 24–27. 57–62

Lin JF, Kung TC, Chang SJ (2008) A reduced code linearity test method for pipelined A/D converters. in Proc. IEEE Asian Test Symposium. Nov 24–27. 111–116

Peralias E, Rueda A, Prieto JA, Huertas JL (1998) DfT & on-line test of high-performance data converters: a practical case. in Proc. IEEE International Test Conference. Oct. 534–540

Provost B, Sinencio ES (2004) A practical self-calibration scheme implementation for pipeline ADC. IEEE Trans Instrum Meas 53(2):448–456

Samid L, Volz P, Manoli Y (2004) A dynamic analysis of a latched CMOS comparator. in Proc. IEEE International Symposium on Circuit and System. 181–184

Ting HW, Lin CW, Liu BD, Chang SJ (2007) Oscillator-based reconfigurable sinusoidal signal generator for ADC BIST. J Electron Test: Theory Appl 23:549–558

Ting HW, Liu BD, Chang SJ (2008) Histogram based testing method for estimating A/D converter performance. IEEE Trans Instrum Meas 57:420–427

Acknowledgment

This work was supported in part by the grant of NSC-99-2221-E-151-064- from National Science Council (NSC), Taiwan.

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: M. Margala

Rights and permissions

About this article

Cite this article

Lin, JF., Ting, HW. Digital Design-for-Diagnosis Method for Error Identification of Pipelined ADCs. J Electron Test 27, 697–709 (2011). https://doi.org/10.1007/s10836-011-5252-5

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-011-5252-5