Abstract

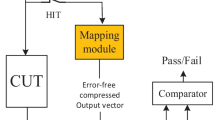

Input vector monitoring concurrent on-line BIST based on multilevel decoding logic is an attractive approach to reduce hardware overhead. In this paper, a novel optimization scheme is proposed for further reducing the hardware overhead of the decoding structure, which refers to improved decoding, input reduction, and simulated annealing inputs swapping approaches. Furthermore, utilizing similar multilevel decoding logic as the responses verifier, a novel cost-efficient input vector monitoring concurrent on-line BIST scheme is presented. The proposed scheme is applicable to the concurrent on-line testing for the CUT, the detail of which can not be obtained, such as hard IP cores. Experimental results indicate that the proposed optimization approaches can significantly reduce the hardware overhead of the decoding structure, and the proposed scheme costs lower hardware than other existing schemes.

Similar content being viewed by others

References

Abramovici M, Breuer M, Friedman A (1994) Digital systems testing and testable design. Wiley, New York

Biswas S, Das SR, Petriu EM (2006) Space compactor design in VLSI circuits based on graph theoretic concepts. IEEE Trans Instrum Meas 55(4):1106–1118

Chen CA, Gupta SK (1998) Efficient BIST TPG design and test set compaction via input reduction. IEEE Trans Comput Aided Des Integr Circuits Syst 17(8):692–705

Chen J-J, Yang C-K, Lee K-J (2003) Test pattern generation and clock disabling for simultaneous test time and power reduction. IEEE Trans Comput Aided Des Integr Circuits Syst 22(3):363–370

Drineas P, Makris Y (2003) Concurrent fault detection in random combinational logic. In: International symposium on quality of electronic design (ISQED), pp 425–430

Drineas P, Makris Y (2003) SPaRe: selective partial replication for concurrent fault-detection in FSMs. IEEE Trans Instrum Meas 52(6):1729–1737

Hansen M, Yalcin H, Hayes JP (1999) Unveiling the ISCAS-85 Benchmarks: A case study in reverse engineering. IEEE Design and Test 16(3):72–80. http://www.eecs.umich.edu/~jhayes. Accessed 27 Sep 2012

Kirkpatrick S (1993) Optimization by simulated annealing. Science 1993(220):671–680

Kochte MA, Zoellin C, Wunderlich HJ (2009) Concurrent self-test with partially specified patterns for low test latency and overhead. In: IEEE European test symposium (ETS), pp 53–58

Kochte MA, Zoellin C, Wunderlich HJ (2010) Efficient concurrent self-test with partially specified patterns. J Electron Test 2010(26):581–594. doi:10.1007/s10836-010-5167-6

Lee HK, Ha DS (1993) On the generation of test patterns for combinational circuits. Dept Elect Eng, Virginia Polytechnic Inst State Univ, Blacksburg, Virginia, Tech Rep, pp 12–93

Sharma R , Saluja K (1988) An implementation and analysis of a concurrent built-in self-test technique. In: 18th international symposium on Fault-Tolerant Computing (FTCS), pp 164–169

Sharma R, Saluja KK (1993) Theory, analysis and implementation of an on-line BIST technique. VLSI Design 1(1):9–22

Saluja KK, Sharma R, Kime C (1987) Concurrent comparative testing using BIST resources. In: Proceedings IEEE international conference on computer-aided design (ICCAD), pp 336–337

Saluja KK, Sharma R, Kime CR (1988) A concurrent testing technique for digital circuits. IEEE Trans Comput Aided Des Integr Circuits Syst 7(12):1250–1260

Voyiatzis I, Halatsis C (2005) A low cost concurrent BIST scheme for increased dependability. IEEE Trans Depend Secure Comput 2(2):150–156

Voyiatzis I, Paschalis A, Gizopoulos D et al (2005) A concurrent built-in self test architecture based on a self-testing RAM. IEEE Trans Reliab 54(1):69–78

Voyiatzis I, Gizopoulos D, Paschalis A et al (2005) A concurrent BIST scheme for on-line/off-line testing based on a pre-computed test set. In: Proceedings IEEE international test conference (ITC), pp 1118–1125

Voyiatzis I, Paschalis A, Gizopoulos D et al (2008) An input vector monitoring concurrent BIST architecture based on a precomputed test set. IEEE Trans Comput 57(8):1012–1022

Voyiatzis I, Gizopoulos D, Paschalis A (2008) A Concurrent BIST scheme exploiting don’t care values. In: Proceedings 16th IFIP/IEEE international conference on very large scale integration (VLSI-SOC), pp 581–588

Voyiatzis I, Gizopoulos D, Paschalis A (2009) An input vector monitoring concurrent BIST scheme exploiting ”X” values. In: Proceedings IEEE international on-line test symposium (IOLTS), pp 206–207

Voyiatzis I (2012) Input vector monitoring on-line concurrent BIST based on mutilevel decoding logic. In: Proceedings IEEE design automation and test in europe conference and exhibition (DATE), pp 1251–1256

Zhou B, Xiao L-Y, Ye Y-Z et al (2011) Optimization of test power and data volume in BIST scheme based on scan slice overlapping. J Electron Test 2011(27):43–56. doi:10.1007/s10836-010-5185-4

Acknowledgments

This work is supported by Hunan Provincial Innovation Foundation For Postgraduate (No. CX2012B031).

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: H. J. Wunderlich

Rights and permissions

About this article

Cite this article

Wu, TB., Liu, HZ., Liu, PX. et al. A Cost-efficient Input Vector Monitoring Concurrent On-line BIST Scheme Based on Multilevel Decoding Logic. J Electron Test 29, 585–600 (2013). https://doi.org/10.1007/s10836-013-5380-1

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-013-5380-1