Abstract

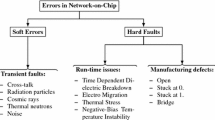

Continuing advances in the processing technology, along with the significant decreases in the feature size of integrated circuits lead to increases in susceptibility to transient errors and permanent faults. Network on Chips (NoCs) have come to address the demands for high bandwidth communication among processing elements. The structural redundancy inherited in NoC-based design can be exploited to improve reliability and compensate for the effects of failures. In this paper, we propose an enhanced fault tolerant microarchitecture with deadlock-free routing for Hierarchical NoCs. The proposed router supplies dynamic Virtual Channel (VC) Allocation, and it employs a high-performance fault tolerant control flow, handling both transient and permanent faults in hierarchical networks without extra retransmission buffer requirements. Experimental results show a significant improvement in reliability as well as decreases in the average latency and energy consumption.

Similar content being viewed by others

References

Alaghi A, Karimi N, Sedghi M, Navabi Z (2007) “Online NoC Switch Fault Detection and Diagnosis Using a High Level Fault Mode,” in Proceedings of International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT), pp. 21–29

Bourduas S and Zilic Z (2007) “A Hybrid Ring/Mesh Interconnect for Network-on-Chip Using Hierarchical Rings for Global Routing,” in Proceedings of Network on Chip Symposium (NOCS), pp.195–204

Dally WJ and Towles B (2001) “Route packets not wires: On-chip interconnection networks,” in Proceedings of Design Automation Conference (DAC), pp. 684–689

Das R, Eachempati S, Mishra AK, Narayanan V, Das CR (2009) “Design and Evaluation of a Hierarchical On-Chip Interconnect for Next-Generation CMPs,” in Proceedings of International Symposium on High Performance Computer Architecture (HPCA), pp. 175–186

Duato J, Yalamanchili S, Nionel L (2003) “Interconnection networks: An engineering approach,” (Morgan Kaufmann Publishers)

Guree A, Ventroux N, David R, Merigot A (2010) “Hierarchical Network-on-Chip for Embedded Many-Core Architectures,” in Proceedings of Network on Chip Symposium (NOCS), pp. 189–196

Holsmark R, Kumar S, Palesi M, Mejia A (2009) “HiRA: A Methodology for Deadlock Free Routing in Hierarchical Networks on Chip,” in Proceedings of Network on Chip Symposium (NOCS), pp. 2–11

Kang YH, Kwon T, and Draper J (2009) “Dynamic Packet Fragmentation for Increased Virtual Channel Utilization in On-Chip Routers,” in Proceedings of International Symposium on Networks-on-Chip (NOCS), pp. 250–255

Karanth Kodi A, Sarathy A, and Louri A (2008) “iDEAL: Inter-Router Dual-function Energy and Area-efficient Links for Network-on-Chip (NoC) Architectures,” in Proceedings of International Symposium on Computer Architecture (ISCA), pp. 241–250

Kim J, Nicopoulos C, Park D, Vijaykrishnan N, Yousif MS, and Das CR (2006) “A Gracefully Degrading and Energy-Efficient Modular Router Architecture for On-Chip Networks,” in Proceedings of International Symposium on Computer Architecture (ISCA)

Kumar A, Kundu P, Singh AP, Peh L and Jha N (2007) “4.6Tbits/s 3.6GHz Single-cycle NoC Router with a Novel Switch Allocator in 65nm CMOS,” in Proceedings of International Conference on Computer Design (ICCD), pp. 63–70

Latif K, Rahmani AM, Nigussie E, Seceleanu T, Radetzki M, Tenhunen H (2013) Partial virtual channel sharing: a generic methodology to enhance resource management and fault tolerance in networks-on-chip. J Electron Test: Theory Appl (Springer-JETTA). doi:10.1007/s10836-013-5389-5

Neishaburi MH and Zilic Z (2009) “Reliability aware NoC router architecture using input channel buffer sharing,” in Proceedings of Great Lake Symposium on VLSI (GLSVLSI), pp. 511–516

Neishaburi MH and Zilic Z (2011) “A Fault Tolerant Hierarchical Network on Chip Router Architecture,” in Proceedings of International Symposium on Defect and Fault Tolerance in VLSI and Nanotechnology Systems (DFT), pp. 445–453

Neishaburi MH and Zilic Z (2011) “ERAVC: Enhanced Reliability Aware NoC Router,” in Proceedings of International Symposium on Quality Electronic Design (ISQED), pp.591–596

Neishaburi MH and Zilic Z (2011) “A distributed AXI-based platform for post-silicon validation,” in Proceedings of IEEE VLSI Test Symposium (VTS), pp. 8 – 13

Neishaburi MH and Zilic Z (2011) “Hierarchical trigger generation for post-silicon debugging,” in Proceedings of IEEE VLSI Design, Automation and Test (VLSI-DAT), pp. 1 – 4

Neishaburi MH and Zilic Z (2013) “NISHA: A fault-tolerant NoC router enabling deadlock-free interconnection of subsets in hierarchical architecture”. J Syst Archit (JSA)

Park D, Nicopoulos C, Kim J, Vijaykrishnan N, Das CT (2006) “Exploring Fault-Tolerant Network-on-Chip Architectures,” in Proceedings of International Conference on Dependable Systems and Networks (DNS), pp. 93–104

Rodrigo S, Flich J, Roca A, Medardoni S, Bertozzi D, Camacho J, Silla F, Dauto J (2011) Cost-efficient on-chip routing implementations for CMP and MPSoC systems. IEEE Trans Comput-Aided Des Integr Circ Syst 30:534–547

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: M. Violante

Rights and permissions

About this article

Cite this article

Neishaburi, M.H., Zilic, Z. A Fault Tolerant Hierarchical Network on Chip Router Architecture. J Electron Test 29, 485–497 (2013). https://doi.org/10.1007/s10836-013-5398-4

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-013-5398-4