Abstract

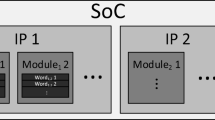

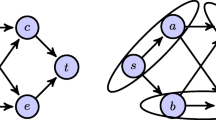

Model-order reduction (MOR) is a typical approach to speed up the post-layout verification simulation step in circuit design. This paper studies the benefits of using circuit partitioning in a complete MOR flow. First, an efficient reduction algorithm package comprising of partitioning, reduction, and realization parts is presented. The reduction flow is then discussed using theoretical analysis and simulations from an array of 65-nm technology node interconnect circuits. It is shown that the reduction efficiency and computational costs quickly worsen with increased circuit size when using a direct projection-based MOR approach. In contrast, by using partitioning, the MOR can retain the scalability of the reduction problem, being computationally lighter and more efficient even with larger circuits. In addition, using partitioning may improve the robustness of the MOR flow in cases with circuits with many ports or sensitive verification simulations.

Similar content being viewed by others

References

Corporation AWR–APLAC (2013) APLAC — Circuit simulation and design tool, Version 8.7 Manuals. AWR–APLAC Corporation, Espoo, Finland

Devgan A, O ′Brien PR (1999) Realizable reduction for RC interconnect circuits. In: Proceedings of IEEE ICCAD

Freund RW (2004) SPRIM: Structure-preserving reduced-order interconnect macromodeling. In: Proceedings of the IEEE ICCAD

Freund RW (2011) The SPRIM algorithm for structure-preserving order reduction. In: Lecture notes in electrical engineering 74, model reduction for circuit simulation. Springer, pp 25–52

Gilbert JR, Moler C, Schreiber R (1992) Sparse matrices in MATLAB: design and implementation. SIAM J Matrix Anal Appl 13 (1): 333–356

Golub GH, Loan CFV (1989) Matrix Computations. Johns Hopkins University Press, Baltimore

Han E-H, Karypis G, Kumar V, Mobasher B (1997) Clustering based on association rule hypergraphs. In: Workshop on research issues on data mining and knowledge discovery

Honkala M, Miettinen P, Roos J (2010) Hierarchical model-order reduction flow. In: Mathematics in industry 14, scientific computing in electrical engineering SCEE 2008. Springer, pp 539–546

Ionutiu R, Rommes J, Schilders WHA (2011). IEEE Trans Comput-Aided Des Integr Circuits Syst 30 (12): 1828–1841

Karypis G, Kumar V (2007). hMETIS, A hypergraph partitioning package (version 1.5.3). http://glaros.dtc.umn.edu/gkhome/metis/hmetis/download

Karypis G, Kumar V (2007). METIS, A software package for partitioning unstructured graphs, partitioning meshes, and computing fill-reducing orderings of sparse matrices (Version 4.0). http://glaros.dtc.umn.edu/gkhome/metis/metis/download

Karypis G (2014) Family of graph and hypergraph partitioning software, Karypis Lab. University of Minnesota, Minneapolis. http://glaros.dtc.umn.edu/gkhome/views/metis

Kundert KS (1995) Designer’s guide to SPICE and SPECTRE. Kluwer Academic Publishers, Norwell

Lee Y-M, Cao Y, Chen T-H, Wang JM, Chen C (2005) HiPrime: Hierarchical and passivity preserved interconnect macromodeling engine for RLCK power delivery. IEEE Trans Comput-Aided Des Integr Circuits Syst 24(6):797–806

Li D, Tan SX-D, Wu L (2009). Itegr VLSI J 42:193–202

Liao H (1995) Scattering-parameter-based macromodel for transient analysis of interconnect networks with nonlinear terminations. PhD thesis Univ., California at Santa Cruz

Miettinen P, Honkala M, Roos J, Valtonen M (2011) PartMOR: Partitioning-based realizable model-order reduction method for RLC circuits. IEEE Trans Comput-Aided Des Integr Circuits Syst 30 (3): 374–387

Miettinen P, Honkala M, Roos J, Valtonen M (2012) Improving model-order methods by singularity exclusion. In: Mathematics in industry 16, scientific computing in electrical engineering SCEE 2010. Springer, pp 387–394

Miettinen P, Honkala M, Roos J, Valtonen M (2012) Partitioning-based reduction of circuits with mutual inductances. In: Mathematics in industry 16, scientific computing in electrical engineering SCEE 2010. Springer, pp 395–404

Miettinen P, Honkala M, Roos J, Valtonen M (2013) Admittance parameter formulation for realizable model-order reduction. In: Proceedings of the 2013 European conference on circuit theory and design (ECCTD), pp 1–4

Miettinen P, Honkala M, Roos J, Valtonen M (2013) Sparsification of dense capacitive coupling if interconnect models. IEEE Trans Very Large Scale Integr (VLSI) Syst 21 (10): 1955–1959

Nanoscale Integration and Modeling Group (2005) Predictive Technology Model. Arizona State University, Tempe. http://ptm.asu.edu

Nicholas H (2008) Functions of Matrices: Theory and Computation Society for industrial and applied mathematics, Philadelphia

Odabasioglu A, Celik M, Pileggi LT (1998). IEEE Trans Comput-Aided Des Integr Circuits Syst 17 (8): 645–654

Palenius T, Roos J (2004) Comparison of reduced-order interconnect macromodels for time-domain simulation. IEEE Trans Microw Theory Tech 52 (9): 2240–2250

Su YF, Wang J, Zeng X, Bai Z, Chiang C, Zhou D (2004) SAPOR: Second-order Arnoldi method for passive order reduction of RCS circuits. In: Proceedings of the IEEE ICCAD

Tan S X-D, Hei L (2007) Advanced model order reduction techniques in VLSI design. NY, New York

Yang F, Zeng X, Su Y, Zhou D (2007) RLCSYN: RLC equivalent circuit synthesis for structure-preserved reduced-order model of interconnect. In: Proceedings of the IEEE ISCAS

Zhao W, Cao Y (2006) New generation of Predictive Technology Model for sub-45 nm early design exploration. IEEE Trans Electron Devices 53 (11): 2816–2823

Zhong G, Koh C, Roy K (2002) On-chip interconnect modeling by wire duplication. In: Proceedings of the IEEE ICCAD

Acknowledgments

This work was partially funded by the Finnish national Graduate School in Electronics, Telecommunications and Automation. Financial support from the Nokia Foundation is acknowledged.

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: V. Champac

Rights and permissions

About this article

Cite this article

Miettinen, P., Honkala, M., Roos, J. et al. Benefits of Partitioning in a Projection-based and Realizable Model-order Reduction Flow. J Electron Test 30, 271–285 (2014). https://doi.org/10.1007/s10836-014-5451-y

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-014-5451-y