Abstract

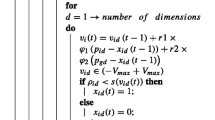

At present, the functional verification of a device represents the highest cost during manufacturing. To reduce that cost, several methods have been suggested. In this work we propose a method which produces a set of binary test sequences by means of a Compact binary Differential Evolution algorithm (Compact-BinDE). The strategy employed is based on the use of coverage models and cost functions in the verification process, which are built with relevant conditions or coverage points representing the full device behavior. The main problem is to cover all difficult situations since the relationships between the test points and the input data in the design are not trivial. The test generation method is included with a proposed verification platform based on a simulation representing a hybrid method. The main contribution of this work is that the method obtains test vector sequences that maximize the coverage percentage on run-time device simulation with an efficient search in the binary domain. Also, different to the previous works that used meta-heuristics, the proposed method by means of the Compact-BinDE algorithm can reduce the simulation time used to obtain test sequences that exercise the coverage points. The results show that the proposed method represents a good alternative to generate test sequences to cover the coverage points during the functional verification.

Similar content being viewed by others

References

Ahn CW, Ramakrishna RS (2003) Elitism-based compact genetic algorithms. IEEE Trans Evol Comput 7(4):367–385

Amer S, Ali H, Sofiene T, Nawwaf K (2006) Automated coverage directed test generation using a cell-based genetic algorithm. In: Proc. IEEE high-level design validation and test workshop, pp 19–26

Armin B (2001) Verifying sequential behavior with model checking. In: Proc. IEEE international ASIC conference, pp 29–32

Bayazit AA, Sharad M (2005) Complementary use of runtime validation and model checking. In: Proc. International Conf. Computer-Aided Design (ICCAD-2005), pp 1049–1056

Bose M, Shin J, Rudnick EM, Dukes T, Abadir M (2001) A genetic approach to automatic bias generation for biased random instruction generation. Evol Comput 2:442–448

Changshou D, Zhao B, Yang Y, Peng H, Wei Q (2011) Novel binary encoding differential evolution algorithm. In: Proc. 2nd international conference: on swarm intelligence, advances in Swarm Intelligence (Springer), pp 416–423

Chen M, Mishra P (2011) Decision ordering based property decomposition for functional test generation. In: Proc. IEEE Design, Automation & Test in Europe (DATE), pp 1–6

Chen W, Wang LC, Bhadra J, Abadir M (2013) Simulation knowledge extraction and reuse in constrained random processor verification. In: Proc. 50th Des Autom Conf (DAC), pp 1–6

Chockler H, Kupferman O, Moshe V (2006) Coverage metrics for formal verification. Int J Softw Tools Technol Transfer 8(4/5):373–386

Corno F, Reorda M, Squillero G, Manzone A, Pincetti A (2000) Automatic test bench generation for validation of RTL-level descriptions: an industrial experience. In: Proc. IEEE Conference on Design, Automation and Test in Europe (DATE), pp 385–389

Cruz AM, Fernandez RB, Lozano HM (2013) Automated functional coverage for a digital system based on a binary differential evolution algorithm. In: Proc. IEEE congress on computational intelligence & 11th Brazilian Congress on Computational Intelligence, pp 92–97

Das S, Suganthan PN (2011) Differential evolution: A survey of the state-of-the-art. IEEE Trans on Evol Comput 15(1):4–31

Fedeli A, Fummi F, Pravadelli G (2007) Properties incompleteness evaluation by functional verification. IEEE Trans Comput 56(4):528–544

Fine S, Avi Z (2003) Coverage directed test generation for functional verification using bayesian networks. Proc. Des Autom Conf 15(5):286–291

Gent K, Hsiao MS (2013) Functional test generation at the RTL using swarm intelligence and bounded model checking. In: Proc. 22nd Asian test symposium, pp 233–238

Grosse D, Kuhne U, Drechsler R (2008) Analyzing functional coverage in bounded model checking. IEEE Trans Comput Aided Des Integr Circuits Systs 27(7):1305–1314

Harik GR, Lobo FG, Goldberg DE (1999) The compact genetic algorithm. IEEE Trans Evolutionary Computation 3(4): 287–297

He X, Han L (2007) A novel binary differential evolution algorithm based on artificial immune system. In: Proc. IEEE Congress on Evolutionary Computation, pp 2267–2272

Hertz S, Sheridan D, Vasudevan S (2013) Mining hardware assertions with guidance from static analysis. IEEE Trans Comput Aided Des Integr Circuits Syst 32(6):952–965

Henzinger TA, Nicollin X, Sifakis J, Yovine S (1992) Symbolic model checking for real-time systems. In: Proc. 7th Annual IEEE Symp Logic in Comput Sci, pp 394–406

Hocine R, Kalla H, Kalla S, Arar C (2012) A methodology for verification of embedded systems based on systemc. In: Proc. IEEE International conference on Complex Systems (ICCS), pp 1–6

Jain J, Narayan A, Fújita M, Sangiovanni-Vincentelli A (1997) A survey of techniques for formal verification of combinational circuits. In: Proc. IEEE International Conf Computer Design, pp 445–454

Jerinic V, Langer J, Heinkel U, Muller D (2006) New methods and coverage metrics for functional verification. In: Proc. IEEE Design, Automation and Test in Europe (DATE), pp 1–6

Kang J, Seth SC, Chang Y-S, Gangaram V (2008) Efficient selection of observation points for functional tests. In: Proc. IEEE 9th international symposium on quality electronic design, pp 236– 241

Kumar JA, Vasudevan S (2012) Verifying dynamic power management schemes using statistical model checking. In: Proc. IEEE Design Automation Conference, pp 574–584

Lachish O, Marcus E, Ur S, Ziv A (2002) Hole Analysis for functional coverage data. In: Proc. 39th Design Automation Conference, pp 807–812

Lefticaru R, Ipate F, Tudose C (2009) Automated model design using genetic algorithms and model checking. In: Proc. IEEE Fourth Balkan Conference in Informatics, pp 79–84

Li M, Hsiao MS (2009) An ant colony optimization technique for abstraction-guided state justification. In: Proc. IEEE International Test Conf., pp 1–10

Mininno E, Neri F, Cupertino F, Naso D (2010) Compact differential evolution. IEEE Trans Evol Comput 15(1):32–54

Neri F, Mininno E (2010) Memetic compact differential evolution for cartesian robot control. IEEE Comput Intell Mag 5 (2):54–65

Oh Y-J, Song G-Y (2011) Simple hardware verification platform using SystemVerilog. In: Proc. IEEE Region 10 Conf., pp 1414–1417

Onwubolu GC, Davendra D (2009) Differential evolution: A handbook for global permutation-based combinatorial optimization. Studies in Computational Intelligence, vol 175, pp 1–226

Pampará G, Engelbrecht AP, Franken N (2006) Binary differential evolution algorithm. In: Proc. IEEE congress on Evolutionary computation, pp 1873–1879

Piziali A (2008) Functional verification coverage measurement and analysis. First edition. Springer, New York

Qin X, Mishra P (2011) Efficient directed test generation for validation of multicore architectures. In: Proc. 12th International Symp Qual Electron Des, pp 1–8

Rancea I, Sgarciu V (2008) Functional verification of digital circuits using a software system. In: IEEE international conference on Automation, quality and testing, Robotics (AQTR), pp 152–157. AQTR:152–157

Raik J, Repinski U, Chepurov A, Hantson H, Ubar R, Jenihhin M (2013) Automated design error debug using high-level decision diagrams and mutation operators. Microprocess Microsyst 37 (4-5):505–513

Romero EL, Strum M, Chau WJ (2013) Manipulation of training sets for improving data mining coverage driven verification. Journal of Electronic Testing, Theory and Applications (JETTA) 29(2):223–236

Shen H, Wei W, Chen Y, Chen B, Guo Q (2008) Coverage directed test generation godson experience. In: Proc. 17th Asian Test Symp, pp 321–326

Serrstou Y, Beroulle V, Robach C (2007) Functional verification of RTL designs driven by mutation testing metrics. In: Proc. 10th Euromicro Conf Digit Syst Des Archit, Methods and Tools, pp 222–227

Storn R, Price K (1997) Differential evolution - A simple and efficient adaptive scheme for global optimization over continuous spaces. J Glob Optim 11(4):341–359

Storn R, Price K (1996) Minimizing the real functions of the ICEC’96 contest by differential evolution. In: Proc. IEEE International Conf Evolutionary computation, pp 842–844

Tasiran S, Keutzer K (2001) Coverage metrics for functional validation of hardware designs. IEEE Des Test Comput 18(4):36–45

Vado P, Savaria Y, Zoccarato Y, Robach C (2000) A methodology for validating digital circuits with mutation testing. In: Proc. international symposium on circuits and systems, vol 1, pp 343–346

Vasudevan S, Sheridan D, Patel S, Tcheng D, Tuohy B, Daniel J (2010) GoldMine: automatic assertion generation using data mining and static analysis. In: Proc. IEEE Design, Automation & Test in Europe Conference & Exhibition (DATE), pp 1530–1591

Vasudevan S, Sheridan D, Patel S, Tcheng D, Tuohy B, Johnson D (2010) GoldMine: automatic assertion generation using data mining and static analysis. In: Proc. Design, Automation and Test in Europe Conf, pp 626–629

Vecchi MP, Kirkpatrick S (1983) Global wiring by simulated annealing. IEEE Trans Comput Aided Des Integr Circuits Syst 2(4):215–222

Wagner I, Bertacco V, Austin T (2007) Microprocessor verification via feedback-adjusted Markov models. Comput Aided Des Integr Circuits Syst 26(6):1126–1138

Wallack JR, Dandapani R (1994) Coverage metrics for functional tests. In: Proc. 12th IEEE VLSI Test Symp, pp 176–181

Xie T, Mueller W, Letombe F (2012) Mutation-analysis driven functional verification of a soft microprocessor. In: Proc. IEEE International SOC Conference (SOCC), pp 283–288

Yu X, Fin A, Fummi F, Rudnick EM (2002) A genetic testing framework for digital integrated circuits. In: Proc. 14th IEEE International Conf on Tools with Artificial Intelligence, (ICTAI), pp 521–526

Acknowledgments

This work has been partially supported by grants under agreements SIP-SIP: 20151454 of Secretaría de Investigación y Posgrado del Instituto Politécnico Nacional (IPN), México. Also this work was supported by Consejo Nacional de Ciencia y Tecnología (CONACyT), México, and Sistema de Becas por Exclusividad (SIBE)-COFAA.

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: P. Mishra

Rights and permissions

About this article

Cite this article

Cruz, A.M., Fernández, R.B., Lozano, H.M. et al. Automated Functional Test Generation for Digital Systems Through a Compact Binary Differential Evolution Algorithm. J Electron Test 31, 361–380 (2015). https://doi.org/10.1007/s10836-015-5540-6

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-015-5540-6