Abstract

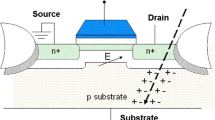

Recent radiation ground testing campaigns of digital designs have demonstrated that the probability for Single Event Transient (SET) propagation is increasing in advanced technologies. This paper presents a hierarchical reliability-aware synthesis framework to design combinational circuits at gate level with minimal area overhead. This framework starts by estimating the vulnerability of the circuit to SETs. This is done by modeling the SET propagation as a Satisfiability problem by utilizing Satisfiability Modulo Theories (SMTs). An all-solution SMT solver is adapted to estimate the soft error rate due to SETs. Different strategies to mitigate SETs are integrated in the proposed framework to selectively harden vulnerable nodes in the design. Both logical and temporal masking factors of the target circuit are improved to harden sensitive paths or sub-circuits, whose SET propagation probability is relatively high. This process is repeated until the desired soft error rate is achieved or a given area overhead constraint is met. The proposed framework was implemented on different combinational designs. The reliability of a circuit can be improved by 64% with less than 20% area overhead.

Similar content being viewed by others

References

Almukhaizim S, Makris Y (2008) Soft error mitigation through selective addition of functionally redundant wires. IEEE Trans Reliab 57(1):23–31

Asadi H, Tahoori MB (2010) Soft error modeling and remediation techniques in asic designs. Microelectron J 41(8):506–522

Bany Hamad G, Hasan SR, Ait Mohamed O, Savaria Y (2014) Modeling, analyzing, and abstracting single event transient propagation at gate level. In: Proceedings IEEE 57th international midwest symposium on circuits and systems (MWSCAS), pp 515– 518

Bany Hamad G, Hasan SR, Ait Mohamed O, Savaria Y (2014b) New insights into the single event transient propagation through static and tspc logic. IEEE Trans Nucl Sci 61(4):1618– 1627

Bany Hamad G, Hasan SR, Ait Mohamed O, Savaria Y (2015) Characterizing, modeling, and analyzing soft error propagation in asynchronous and synchronous digital circuits. Microelectron Reliab 55(1):238–250

Bany Hamad G, Kazma G, Ait Mohamed O, Savaria Y (2016) Efficient and accurate analysis of single event transients propagation using smt-based techniques. In: International conference on computer aided design (ICCAD), p 54

Barrett C, Sebastiani R, Seshia S, Tinelli C (2009) Satisfiability modulo theories. Handbook of satisfiability 185:825–885

Basu K, Mishra P, Patra P (2013) Observability-aware directed test generation for soft errors and crosstalk faults. In: Proceedings international conference on VLSI design and 12th international conference on embedded systems, pp 291–296

Chakraborty S, Meel KS, Mistry R, Vardi MY (2015) Approximate probabilistic inference via word-level counting. arXiv:151107663

Daga A et al (2002) Automated timing model generation. In: Proceedings Design Automation Conference (DAC), pp 146–151

Dotan Y, Levison N, Lilja D (2011) Fault tolerance for nanotechnology devices at the bit and module levels with history index of correct computation. IET Comput Digit Tech 5(4):221–230

El-Maleh A, Daud K (2015) Simulation-based method for synthesizing soft error tolerant combinational circuits. IEEE Trans Reliab 64(3):935–948

El-Maleh AH, Al-Qahtani AS (2014) A finite state machine based fault tolerance technique for sequential circuits. Microelectron Reliab 54(3):654–661

El-Maleh AH, Oughali FC (2014) A generalized modular redundancy scheme for enhancing fault tolerance of combinational circuits. Microelectron Reliab 54(1):316–326

Ermon S, Gomes CP, Selman B (2012) Uniform solution sampling using a constraint solver as an oracle. arXiv:12104861

Ferlet-Cavrois V, Massengill L, Gouker P (2013) Single event transients in digital CMOS—A review. IEEE Trans Nucl Sci 60(3):1767–1790

Ferrick AM, Neil B, Aizer A, Chinitz L (2008) Cosmic radiation induced software electrical resets in icds during air travel. Heart Rhythm 5(8):1201–1203

Gogate V, Dechter R (2011) Samplesearch: importance sampling in presence of determinism. Artif Intell 175(2):694–729

Krishnaswamy S, Plaza SM, Markov IL, Hayes JP (2007) Enhancing design robustness with reliability-aware resynthesis and logic simulation. In: Proceedings international conference on computer aided design (ICCAD), pp 149–154

Kuo YH, Peng HK, Wen CHP (2010) Accurate statistical soft error rate (sser) analysis using a quasi-monte carlo framework with quality cell models. In: Proceedings International Symposium on Quality Electronic Design (ISQED), pp 831–838

Liang J, Han J, Lombardi F (2013) Analysis of error masking and restoring properties of sequential circuits. IEEE Trans Comput 62(9):1694–1704

Limbrick DB, Mahatme N, Robinson WH, Bhuva BL (2013) Reliability-aware synthesis of combinational logic with minimal performance penalty. IEEE Trans Nucl Sci 60(4):2776–2781

Loiacono C, Marco Palena P, Pasini D, Patti SQ, Ricossa S, Vendraminetto D, Baumgartner J (2013) Fast cone-of-influence computation and estimation in problems with multiple properties. In: Proceedings IEEE/ACM Design Automation & Test in Europe Conference (DATE), pp 803–806

Mohanram K, Touba NA (2003) Partial error masking to reduce soft error failure rate in logic circuits. In: Proceedings IEEE International Symposium on Defect and Fault Tolerance (DFT) in VLSI Systems, pp 433–440

Platzker D, Kaady JA, Kapoor A (2014) Single event upset mitigation for electronic design synthesis. US Patent App 14(/220): 696

Rajaraman R, Kim J, Vijaykrishnan N, Xie Y, Irwin M (2006) Seat-la: a soft error analysis tool for combinational logic. In: Proceedings international conference on VLSI design. IEEE, Piscataway, pp 4–8

Rao R, Chopra K, Blaauw D, Sylvester D (2006) An efficient static algorithm for computing the soft error rates of combinational circuits Proceedings IEEE/ACM design automation & test in europe conference (DATE), vol 1, pp 1–6

Rubinstein R (2013) Stochastic enumeration method for counting np-hard problems. Methodol Comput Appl Probab 15(2):249– 291

Sheikh AT, El-Maleh AH, Elrabaa ME, Sait SM (2017) A fault tolerance technique for combinational circuits based on selective-transistor redundancy. IEEE Trans Very Large Scale Integr VLSI Syst 25(1):224–237

Siewiorek D, Swarz R (2014) Reliable Computer Systems: Design and Evaluatuion. Digital Press

Stine J, Castellanos I, Wood M, Henson J, Love F, Davis W, Franzon P, Bucher M, Basavarajaiah S, Oh J, Jenkal R (2007) Freepdk: An open-source variation-aware design kit. In: Proceedings IEEE International Conference on Microelectronic Systems Education (MSE), pp 173–174

Tosun S, Mansouri N, Arvas E, Kandemir M, Xie Y (2005) Reliability-centric high-level synthesis. In: Proceedings design, automation and test in Europe (DATE), pp 1258–1263

Wei W, Selman B (2005) A new approach to model counting. In: Proceedings international conference on theory and applications of satisfiability testing. Springer, Berlin, pp 324–339

Wirth G, L Kastensmidt F, Ivandro R (2008) Single event transients in logic circuits load and propagation induced pulse broadening. IEEE Trans Nucl Sci 55(6):2928–2935

Zaremba T, Jakobsen AR, Søgaard M, Thøgersen AM, Riahi S (2015) Radiotherapy in patients with pacemakers and implantable cardioverter defibrillators: a literature review. Europace Journal 18(4):479–491

Zhou Q, Mohanram K (2004) Transistor sizing for radiation hardening. In: Proceedings international reliability physics symposium proceedings. IEEE, pp 310–315

Author information

Authors and Affiliations

Corresponding author

Additional information

Responsible Editor: N. A. Touba

Rights and permissions

About this article

Cite this article

Hamad, G.B., Ait Mohamed, O. & Savaria, Y. Formal Methods Based Synthesis of Single Event Transient Tolerant Combinational Circuits. J Electron Test 33, 607–620 (2017). https://doi.org/10.1007/s10836-017-5682-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-017-5682-9