Abstract

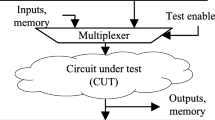

This study applies artificial neural networks (ANNs) to increase stuck-at and delay fault coverage of logic built-in self-test (LBIST) through test point insertion (TPI). Increasing TPI quality is essential for modern logic circuits, but the computational requirements of current TPI heuristics scale unfavorably against increasing circuit complexity, and heuristics that evaluate a TPs quality can mask the effects of delay-causing defects that are common in modern technologies. Previous studies show ANNs giving substantial benefits to a wide array of electronic design automation (EDA) problems, including design-for-test (DFT), but their application to various DFT problems is in its infancy. This study demonstrates how to train an ANN to evaluate test points (TPs) and demonstrates a substantial decrease in TPI computation time compared to existing heuristics while delivering comparable stuck-at and delay fault coverage.

Similar content being viewed by others

Data Availability

The datasets generated during and/or analyzed during the current study are available from the corresponding author on reasonable request.

References

Acero C, Feltham D, Liu Y, Moghaddam E, Mukherjee N, Patyra M, Rajski J, Reddy SM, Tyszer J, Zawada J (2017) Embedded Deterministic Test Points. IEEE Trans Very Large Scale Integr VLSI Syst 25(10):2949–2961

Brglez F (1984) On Testability Analysis of Combinational Networks. In: Proc IEEE Intl Symp Circuits and Systems (ISCAS), Montreal, Quebec, Canada, May 1984, vol 1, pp 221–225

Brglez F, Fujiwara H (1985) A Neutral Netlist of 10 Combinational Benchmark Circuits and a Targeted Translator in FORTRAN. In: Proc. IEEE Intl. Symp. Circuits and Systems (ISCAS), Kyoto, Japan, pp 663–698

Chern M et al (2019) Improving Scan Chain Diagnostic Accuracy Using Multi-stage Artificial Neural Networks. In: Proc. 24th Asia and South Pacific Design Automation Conf., Tokyo, Japan, Jan 2019, pp 341–346

Davidson S (1999) ITC’99 Benchmark Circuits - Preliminary Results. In: Proc Intl Test Conf (ITC), Atlantic City, NJ, USA, Sep. 1999, p 1125

Ghosh S, Bhunia S, Raychowdhury A, Roy K (2006) A Novel Delay Fault Testing Methodology Using Low-Overhead Built-In Delay Sensor. IEEE Trans Comput Aided Des Integr Circuits Syst 25(12):2934–2943

Gómez LR, Wunderlich H (2016) A Neural-Network-Based Fault Classifier. In: Proc. 25th IEEE Asian Test Symposium (ATS), Hiroshima, Japan, Nov. 2016, pp 144–149

Haykin SO (2008) Neural Networks and Learning Machines, 3rd edn. Pearson, New York

Karystinos GN, Pados DA (2000) On Overfitting, Generalization, and Randomly Expanded Training Sets. IEEE Trans Neural Netw 11(5):1050–1057

Kingma DP, Ba J (2019) Adam: A Method for Stochastic Optimization. Dec. 2014. http://arxiv.org/abs/1412.6980. Accessed 8 Apr 2019

Ma Y, Ren H, Khailany B, Sikka H, Luo L, Natarajan K, Yu B (2019) High Performance Graph Convolutional Networks with Applications in Testability Analysis. In: Proc. 56th Annual Design Automation Conference (DAC), New York, NY, USA, Article no. 18, pp 1–6

Menon A, Mehrotra K, Mohan CK, Ranka S (1996) Characterization of a Class of Sigmoid Functions with Applications to Neural Networks. Neural Netw 9(5):819–835

Millican SK, Sun Y, Roy S, Agrawal VD (2019) Applying Neural Networks to Delay Fault Testing: Test Point Insertion and Random Circuit Training. In: Proc. 28th Asian Test Symp. (ATS), Kolkata, India, pp 13–18

Moghaddam E, Mukherjee N, Rajski J, Solecki J, Tyszer J, Zawada J (2019) Logic BIST with Capture-per-Clock Hybrid Test Points. IEEE Trans Comput Aided Des Integr Circuits Syst 38(6):1028–1041

Nag PK, Gattiker A, Wei S, Blanton RD, Maly W (2002) Modeling the Economics of Testing: a DFT Perspective. IEEE Des Test Comput 19(1):29–41

Nigh P, Gattiker A (2000) Test Method Evaluation Experiments and Data. In: Proc. International Test Conference (ITC), Atlantic City, NJ, USA, pp 454–463

Pomeranz I (2017) Computation of Seeds for LFSR-Based n-Detection Test Generation. ACM Trans Des Autom Electron Syst 22(2):1–13

Rajski J, Tyszer J (1998) Arithmetic Built-in Self-test for Embedded Systems. Prentice-Hall Inc, Upper Saddle River, NJ, USA

Roy S, Stiene B, Millican SK, Agrawal VD (2019) Improved Random Pattern Delay Fault Coverage Using Inversion Test Points. In: Proc. IEEE 28th North Atlantic Test Workshop (NATW), Burlington, VT, USA, pp 1–6

Savir J (1992) Skewed-Load Transition Test: Part I, Calculus. In: Proc. Intl. Test Conf. (ITC), Baltimore, MD, USA, Sep. 1992, pp 705–713

Seshan K (2018) Reliability Issues: Reliability Imposed Limits to Scaling. In: Seshan K, Schepis D (eds) Handbook of Thin Film Deposition, 4th edn. William Andrew Publishing, pp 43–62

Sun Y, Millican SK (2019) Test Point Insertion Using Artificial Neural Networks. In: Proc. IEEE Computer Society Annu. Symp. VLSI (ISVLSI), Miami, FL, USA, pp 253–258

Sun Y, Millican SK, Agrawal VD (2020) Special Session: Survey of Test Point Insertion for Logic Built-in Self-test. In: Proc. IEEE VLSI Test Symposium (VTS), San Diego, CA, USA, pp 1–6

Sziray J (2011) Test Generation and Computational Complexity. In: Proc. IEEE 17th Pacific Rim Intl. Symp. Dependable Computing, Pasadena, CA, USA, pp 286–287

Tamarapalli N, Rajski J (1996) Constructive Multi-phase Test Point Insertion for Scan-based BIST. In: Proc Intl Test Conf (ITC), Washington, DC, USA, pp 649–658

Tsai H-C, Cheng K-T, Lin C-J, Bhawmik S (1997) A Hybrid Algorithm for Test Point Selection for Scan-based BIST. In: Proc. 34th ACM/IEEE Design Automation Conf. (DAC), Anaheim, CA, USA, pp 478–483

Xiang D, Wen X, Wang L-T (2017) Low-Power Scan-Based Built-In Self-Test Based on Weighted Pseudorandom Test Pattern Generation and Reseeding. IEEE Trans Very Large Scale Integr VLSI Syst 25(3):942–953

Author information

Authors and Affiliations

Corresponding author

Ethics declarations

Conflicts of Interests

The authors have no relevant financial or non-financial interests to disclose.

Additional information

Responsible Editor: E. Amyeen

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Sun, Y., Millican, S.K. Applying Artificial Neural Networks to Logic Built-in Self-test: Improving Test Point Insertion. J Electron Test 38, 339–352 (2022). https://doi.org/10.1007/s10836-022-06016-9

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s10836-022-06016-9