Abstract

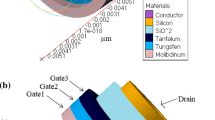

To keep continue the miniaturization of VLSI technology a Trimetal asymmetrical gate all around (TG-GAA) device is proposed to narrow the short channel effects of the scaling down of devices in terms of the improved subthreshold slope by reducing the leakage current up to 2.37E−13 A and have the better control on the channel at lower supply voltages from 0.1 V to 1 V. The analytical electrical field distribution, channel length characterization and potential profile of the proposed device based on Gate all around Silicon nanowire MOSFET channel are enclosed by the Trimetal gate have been observed Using 2-D Poisson equation by considering parabolic approximation with appropriate boundary condition in cylindrical coordinates. Further subthreshold drain current model is derived by applying derived potential profile at subthreshold condition by considering the diffusion transportation. The surface & centre potential has been carried out to satisfy the basic optimum parameters for this new structure, which further supports that the DIBL effects was been minimized and observed that by reducing silicon thickness at (tSi =5 nm) lower leakage current 2.37E-13A and improved drain current(Id) of 2.159E-05A is obtained. Further proposed device exhibit decline DIBL of 23.3 mV/V, magnificent subthreshold slope 63.5 mV/decade and improved higher threshold voltage improved ON/OFF ratio. Additionally, well agreement has been observed between the derived 2-D analytical model with the simulated results obtained from numerical simulator Cogenda visual TCAD.

Similar content being viewed by others

References

Arora N (1993) MOSFET models for VLSI circuit simulation. Springer-Verlag, Wien

Colinge J-P (2004) Multiple- gate SOI MOSFETs. Solid State Electronics 48:897–905

Committee IR et al. (2007) International technology roadmap for semiconductors, 2007 Edition, Executive Summary, 1-86

Dennard N (1972) Design of micron MOS switching devices. IEDM Tech Dig, pp:168–170

Dubey S, Santra A, Saramekala G, Kumar M, Tiwari PK (2013) An analytical threshold voltage model for triple-material cylindrical gate-all-around (TM-CGAA) MOSFETs. IEEE Trans Nanotechnol 12(5):766–774

El Hamid HA, Iniguez B, Guitart JR (2007) Analytical model of the threshold voltage and sub threshold swing of undoped cylindrical gate-all-around-based MOSFETs. IEEE Transactions on Electron Devices 54(3):572–579

Genius : 3D Parallel Device Simulator, Product Brochure | Application Examples

Hiroshi I, Kenji N (2011) Si nanowire FET and its modeling, Science China Press and Springer-Verlag Berlin Heidelberg 54(5): 1004-1011

Iniguez B, Fjeldly A, Lázaro A, Danneville F, and Deen MJ (2006) Compact-modeling solutions for nanoscale double-gate and gate-all-around MOSFETs. IEEE Trans Electron Dev 53(9)

Iniguez B, Hamid HA (2005) Compact model for multiple-gate SOI MOSFETs. NSTI-Nanotech

Karbalaei M, Dideban D, Heidari H (2020) Impact of high-k gate dielectric with different angles of coverage on the electrical characteristics of gate-all-around field effect transistor: a simulation study. Results in Physics 16:102823

Kaur A, Rajesh M, Amit S (2019) Hetero-dielectric oxide engineering on dopingless gate all around nanowire MOSFET with Schottky contact source/drain. Int J Electron Commun (AEU) 111:152–888

Kranti A, Haldar S, Gupta R (2001) An accurate 2D analytical model for short channel thin film fully depleted cylindrical/surrounding gate (CGT/SGT)MOSFET. Microelectron J 32(4):305–313

Lee Y, Park GH, Choi B, Yoon J, Kim HJ, Kim DH, Choi SJ (2020) Design study of the gate-all-around silicon nanosheet MOSFETs. Semicond Sci Technol 35(3):03LT01

Moore GE (1975) Progress in digital integrated electronics. International Electron Devices

Moore GE et al. (1965) Cramming more components onto integrated circuits

Narula V, Agarwal M (2019) Enhanced performance of double gate junctionless field effect transistor by employing rectangular core-shell architecture. Semicond Sci Technol 34:105014

Pal A, Sarkar A (2014) Analytical study of dual material surrounding gate MOSFET to suppress short channel effects (SCEs). Eng Sci Technol 17:205–212

Pradhan KP, Sahu PK (2015) Analytical modeling of threshold voltage for cylindrical gate all around MOSFETs using center potential. Ain Shams Eng J 6:1171–1177

Rahou FZ, Guen Bouazza A, Bouazza B (2016) Performance improvement of pi-gate SOI MOSFET transistor using high-k dielectric with metal gate. IETE J Res 62(3):331–338

Rewari S, Nath V, Subhasis H, Deswal SS, Gupta RS (2017) Gate-induced drain leakage reduction in cylindrical dual-metal hetero-dielectric gate all around MOSFET. IEEE Trans Electron Devices 65(1):3–10

Suh CH (2011) Two-dimensional analytical model for deriving the threshold voltage of a short channel fully depleted cylindrical/surrounding gate MOSFETs. J Semiconduct Technol Sci 11(2)

Sun Y, Tang Y, Li X, Shi Y, Wang T, Xu J, Liu Z (2020) Analysis of gate-induced drain leakage in gate-all-around nanowire transistors. J Comput Electron 1-8

Sze SM, Ng Kwok K (2007) Physics of semiconductor devices, 3rd edn. Wiley, Hoboken, pp 247–328

Tiwari PK, Samoju VR (2016) Analytical modeling of threshold voltage for symmetrical silicon nano-tube field-effect-transistors. J Comput Electron 15:516–524

Author information

Authors and Affiliations

Corresponding author

Additional information

Publisher’s note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

About this article

Cite this article

Rathee, D.S., Yadav, R. & Ahuja, K. Reduction of drain induced barrier lowering by optimization Trimetal- GAA -Si -NW MOSFET in multimedia tools. Multimed Tools Appl 81, 19849–19862 (2022). https://doi.org/10.1007/s11042-021-11518-3

Received:

Revised:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11042-021-11518-3