Abstract

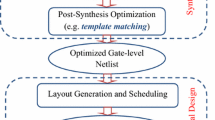

Quantum circuit design flow consists of two main tasks: synthesis and physical design. Addressing the limitations imposed on optimization of the quantum circuit objectives because of no information sharing between synthesis and physical design processes, we introduced the concept of “physical synthesis” for quantum circuit flow and proposed a technique for it. Following that concept, in this paper we propose a new technique for physical synthesis using auxiliary qubit selection to improve the latency of quantum circuits. Moreover, it will be shown that the auxiliary qubit selection technique can be seamlessly integrated into the previously introduced physical synthesis flow. Our experimental results show that the proposed technique decreases the average latency objective of quantum circuits by about 11% for the attempted benchmarks.

Similar content being viewed by others

Explore related subjects

Discover the latest articles, news and stories from top researchers in related subjects.References

Lloyd, S.: Quantum-mechanical computers. Sci. Am. (273), 44–49 (1995)

Feynman R.P.: Quantum mechanical computers. Found. Phys. 16, 507 (1986)

Shor P.: Polynomial time algorithms for prime factorization and discrete logarithms on a quantum computer. SIAM J. Comput. 26(5), 1484–1509 (1997)

Grover, L.: A fast quantum mechanical algorithm for database search. In: Proceeding of ACM Symposium on Theory of Computing, pp. 212–219 (1996)

Zalka, C.: Simulating quantum systems on a quantum computer. In: Proceeding of Mathematical, Physical and Engineering Sciences, pp. 313–322 (1998)

Wootters W.K., Zurek W.H.: A single quantum cannot be cloned. Nature 299, 802–803 (1982)

Schrödinger E.: The present situation in quantum mechanics. Naturewiss 48, 807–812 (1935)

Welsh D.: Codes and Cryptography. Oxford University Press, Oxford (1988)

http://www.magiqtech.com/MagiQ/Home.html, accessed on 2010-2-28

http://www.idquantique.com, accessed on 2010-2-28

Whitney, M., Isailovic, N., Patel, Y., Kubiatowicz, J.: Automated generation of layout and control for quantum circuits. In: Proceeding of Computing Frontiers, pp. 83–94 (2007)

Alpert, C.J., Chu, C.: Physical synthesis comes of age. In: Proceedings of International Conference on Computer-Aided Design (ICCAD), pp. 246–249 (2007)

Mohammadzadeh, N., Sedighi, M., Saheb Zamani, M.: Quantum physical synthesis: improving physical design by netlist modifications. Accepted for publication in Elsevier Microelectronics Journal

Häffner, H., Roos, C.F., Blatt, R.: Quantum computing with trapped ions. Physics Reports, pp. 155–203 (2008)

Kielpinski D., Monroe C., Wineland D.: Architecture for a large-scale ion-trap quantum computer. Nature 417, 709–711 (2002)

Svore K., Aho A., Cross A., Chuang I., Markov I.: A layered software architecture for quantum computing design tools. Computer 39(1), 74–83 (2006)

Svore, K., Cross, A., Aho, A., Chuang, I., Markov, I.: Toward a software architecture for quantum computing design tools. In: Proceedings of the 2nd International Workshop on Quantum Programming Languages (QPL), pp. 145–162 (2004)

Balensiefer, S., Kreger-Stickles, L., Oskin, M.: QUALE: quantum architecture layout evaluator. In: Proceedings of SPIE the international society for optical endineering 5815, pp. 103–114 (2005)

Balensiefer, S., Kregor-Stickles, L., Oskin, M.: An evaluation framework and instruction set architecture for ion-trap based quantum micro-architectures. In: Proceedings of International Symposium on ComputerArchitecture (ISCA), pp. 186–196 (2005)

Omer, B.: Quantum programming in qcl, Master thesis, Technical University of Vienna (2000)

Yang T., Gerasoulis A.: List scheduling with and without communication delays. J. Parallel Comput. 19(12), 1321–1344 (1993)

Metodi, T., Thaker, D., Cross, A., Chong, F., Chuang, I.: A quantum logic array microarchitecture: scalable quantum data movement and computation. In: Proceedings of the 38th International Symposium on Microarchitecture (MICRO), pp. 305–318 (2005)

Thaker D., Metodi, T., Cross, A., Chuang, I., Chong, F.: Quantum memory hierarchies: efficient designs to match available parallelism in quantum computing. In: Proceedings of the 33rd International Symposium on Computer Architecture (ISCA), pp. 378–390 (2006)

Metodi, T., Thaker, D., Cross, A., Chong, F., Chuang, I.: Scheduling physical operations in a quantum information processor. In: Proceedings of SPIE Defense and Security Symposium, 6244. 62440T.1–62440T.12 (2006)

Hucul D., Yeo M., Olmschenk S., Monroe C., Hensinger W., Rabchuk J.: On the transport of atomic ions in linear and multidimensional ion trap arrays. J. Quantum Inf. Comput. 8(6), 0501–0578 (2008)

Kim J., Pau S., Ma Z., McLellan H., Gages J., Kornblit A., Slusher R.: System design for large-scale ion trap quantum information processor. J. Quantum Inf. Comput. 5(7), 515–537 (2005)

Chiaverini J. et al.: Surface-electrode architecture for ion-trap quantum information processing. J. Quantum Inf. Comput. 5(5), 419–439 (2005)

Nielsen M.A., Chuang I.L.: Quantum Computation and Quantum Computation. Cambridge University Press, Cambridge (2000)

Barenco A. et al.: Elementary gates for quantum computation. Phys. Rev. A 52, 3457–3467 (1995)

Saeedi M., Mohammadzadeh N., sedighi M., Saheb Zamani M.: Towards a thorough set of metrics for quantum circuit synthesis. Int. J. Phys. 1(2), 9–22 (2008)

Cross A.: Synthesis and evaluation of fault-tolerant quantum computer architectures. Ph.D. Thesis, Massachusetts Institute of Technology (2005)

Whitney, M., Isailovic, N., Patel, Y., Kubiatowicz, J.: A fault tolerant, area efficient architecture for Shor’s factoring algorithm. ISCA’09 (2009)

Maslov D., Dueck, G., Scott, N.: Reversible logic synthesis benchmarks page. http://www.cs.uvic.ca/~dmaslov/

Robert, W. et al.: Quiver: an online tool for reversible quantum circuit visualization and verification. http://www.revlib.org/tools.php, accessed on 2010-2-28

IBM Rational software, Version 2003, www.ibm.com/software/rational, accessed on 2010-2-28

Author information

Authors and Affiliations

Corresponding author

Rights and permissions

About this article

Cite this article

Mohammadzadeh, N., Zamani, M.S. & Sedighi, M. Auxiliary qubit selection: a physical synthesis technique for quantum circuits. Quantum Inf Process 10, 139–154 (2011). https://doi.org/10.1007/s11128-010-0183-0

Received:

Accepted:

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11128-010-0183-0