Abstract

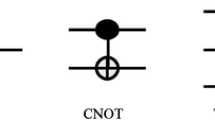

As a result of the recent development of quantum computers, there has been a rise in interest in both reversible logic synthesis and optimization strategies. Because every quantum operation is intrinsically reversible, there is a significant desire for research to create and optimize reversible circuits. This work suggests two novel reversible blocks with a low quantum cost. The reversible blocks are synthesized by an available synthesis technique that produces a grid list of multiple-control Toffoli gates. Then, the Toffoli-based grid is subjected to various optimization techniques, after which it is converted into a netlist of elementary quantum gates taken from the NCV (NOT, CNOT, Controlled-V, and Controlled-V+) library. In addition, a suggestion is presented for the creation of an unsigned multiplier that makes use of the functional blocks that are already available in the system. It has been found that the suggested designs are superior in terms of reversible metrics compared to the most cutting-edge techniques. Compared to recent works, the unsigned multiplier results in average savings of 14.43% for the quantum cost, 27.34% for the garbage output, and 23.29% for the constant input.

Similar content being viewed by others

Availability of data and materials

Not applicable.

References

Balynskiy, M., Chiang, H., Gutierrez, D., Kozhevnikov, A., Filimonov, Y., Khitun, A.: Reversible magnetic logic gates based on spin wave interference. J. Appl. Phys. 123(14), 144501 (2018)

Landauer, R.: Irreversibility and heat generation in the computing process. IBM J. Res. Dev. 5(3), 183–191 (1961)

Bennett, C.H.: Logical reversibility of computation. IBM J. Res. Dev. 17(6), 525–532 (1973)

Maslov, D., Dueck, G.W.: Reversible cascades with minimal garbage. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 23(11), 1497–1509 (2004)

Jayashree, H., Thapliyal, H., Agrawal, V.K.: Design of dedicated reversible quantum circuitry for square computation. In: 2014 27th International Conference on VLSI Design and 2014 13th International Conference on Embedded Systems, pp. 551–556. IEEE (2014)

Feynman, R.P.: Quantum mechanical computers. Opt. News 11(2), 11–20 (1985)

Noorallahzadeh, M., Mosleh, M.: Efficient designs of reversible latches with low quantum cost. IET Circuits Devices Syst. 13(6), 806–815 (2019)

Noorallahzadeh, M., Mosleh, M., Ahmadpour, S.-S.: Efficient designs of reversible synchronous counters in nanoscale. Circuits Syst. Signal Process. 40(11), 5367–5380 (2021)

Noorallahzadeh, M., Mosleh, M.: Efficient designs of reversible shift register circuits with low quantum cost. J. Circuits Syst. Comput. 30(12), 2150215 (2021)

Noorallahzadeh, M., Mosleh, M.: Efficient designs of reversible BCD to EX-3 converter with low quantum cost in nanoscale. Int. J. Quantum Inf. 18(05), 2050020 (2020)

Noorallahzadeh, M., Mosleh, M., Ahmadpour, S.S., Pal, J., Sen, B.: A new design of parity preserving reversible Vedic multiplier targeting emerging quantum circuits. Int. J. Numer. Model. Electron. Netw. Devices Fields (2023). https://doi.org/10.1002/jnm.3089

Thapliyal, H., Ranganathan, N.: A new reversible design of BCD adder. In: 2011 Design, Automation and Test in Europe, pp. 1–4. IEEE (2011)

Toffoli, T.: Reversible computing. In: International Colloquium on Automata, Languages, and Programming, pp. 632–644. Springer (1980)

Feynman, R.P.: Quantum mechanical computers. Found. Phys. 16(6), 507–532 (1986)

Miller, D.M., Maslov, D., Dueck, G.W.: A transformation based algorithm for reversible logic synthesis. In: Proceedings 2003. Design Automation Conference (IEEE Cat. No. 03ch37451), pp. 318–323. IEEE (2003)

Kole, A., Hillmich, S., Datta, K., Wille, R., Sengupta, I.: Improved mapping of quantum circuits to IBM QX architectures. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 39(10), 2375–2383 (2019)

Soeken, M., Sasanian, Z., Wille, R., Miller, D.M., Drechsler, R.: Optimizing the mapping of reversible circuits to four-valued quantum gate circuits. In: 2012 IEEE 42nd International Symposium on Multiple-Valued Logic, pp. 173–178. IEEE (2012)

Zhou, R., Shi, Y., Cao, J.: Transistor realization of reversible “ZS” series gates and reversible array multiplier. Microelectron. J. 42(2), 305–315 (2011)

Dutta, S., Bhattacharjee, D., Chattopadhyay, A.: Quantum circuits for Toom–Cook multiplication. Phys. Rev. A 98(1), 012311 (2018)

Barenco, A., et al.: Elementary gates for quantum computation. Phys. Rev. A 52(5), 3457 (1995)

Nielsen, M.A., Chuang, I.: Quantum Computation and Quantum Information. American Association of Physics Teachers, College Park (2002)

Hung, W.N., Song, X., Yang, G., Yang, J., Perkowski, M.: Optimal synthesis of multiple output boolean functions using a set of quantum gates by symbolic reachability analysis. IEEE Trans. Comput. Aided Des. Integr. Circuits Syst. 25(9), 1652–1663 (2006)

Nowrin, S., Jamal, L., Tasnim, H.: An efficient approach to design a reversible signed multiplier. In: TENCON 2014–2014 IEEE Region 10 Conference, pp. 1–6. IEEE (2014)

Haghparast, M., Navi, K.: A novel reversible BCD adder for nanotechnology based systems (2008.)

Thapliyal, H., Srinivas, M.: Novel reversible multiplier architecture using reversible TSG gate (2006). arXiv preprint https://arxiv.org/abs/cs/0605004

Shams, M., Haghparast, M., Navi, K.: Novel reversible multiplier circuit in nanotechnology. World Appl. Sci. J. 3(5), 806–810 (2008)

Banerjee, A., Pathak, A.: An analysis of reversible multiplier circuits (2009). arXiv preprint http://arxiv.org/abs/0907.3357

Bhagyalakshmi, H., Venkatesha, M.: An improved design of a multiplier using reversible logic gates. Int. J. Eng. Sci. Technol. 2(8), 3838–3845 (2010)

Haghparast, M., Mohammadi, M., Navi, K., Eshghi, M.: Optimized reversible multiplier circuit. J. Circuits Syst. Comput. 18(02), 311–323 (2009)

Islam, M.S., Rahman, M.M., Begum, Z., Hafiz, M.Z.: Low cost quantum realization of reversible multiplier circuit. Inf. Technol. J. 8(2), 208–213 (2009)

PourAliAkbar, E., Mosleh, M.: An efficient design for reversible wallace unsigned multiplier. Theor. Comput. Sci. 773, 43–52 (2019)

Ehsanpour, M., Moallem, P.: A novel design of reversible multiplier circuit. Int. J. Eng. 26(6), 577–586 (2013)

Madhulika, C., Nayak, V.S.P., Prasanth, C., Praveen, T.H.S.: Design of systolic array multiplier circuit using reversible logic. In: 2017 2nd IEEE International Conference on Recent Trends in Electronics, Information and Communication Technology (RTEICT), pp. 1670–1673. IEEE (2017)

Afrin, S., Shihab, F., Sworna, Z.T.: Two novel design approaches for optimized reversible multiplier circuit. In: 2019 IEEE International WIE Conference on Electrical and Computer Engineering (WIECON-ECE), pp. 1–4. IEEE (2019)

Rather, T.A., Ahmed, S., Kakkar, V.: Modelling and simulation of a reversible quantum logic based 4× 4 multiplier design for nanotechnology applications. Int. J. Theor. Phys. 59(1), 57–67 (2020)

Autade, P.P., Turkane, S.M., Deshpande, A.A.: Design of multipliers using reversible logic and toffoli gates. In: 2022 International Conference on Emerging Smart Computing and Informatics (ESCI), pp. 1–4. IEEE (2022)

Akshobhya Jamadagni, K.R., Sakkara, S., Komal, M.: A novel, scalable N* N reversible logic multiplier design. In: 2022 3rd International Conference on Intelligent Engineering and Management (ICIEM), pp. 249–255. IEEE (2022)

Author information

Authors and Affiliations

Corresponding authors

Ethics declarations

Conflict of interest

The authors declare that they have no conflict of interest.

Additional information

Publisher's Note

Springer Nature remains neutral with regard to jurisdictional claims in published maps and institutional affiliations.

Rights and permissions

Springer Nature or its licensor (e.g. a society or other partner) holds exclusive rights to this article under a publishing agreement with the author(s) or other rightsholder(s); author self-archiving of the accepted manuscript version of this article is solely governed by the terms of such publishing agreement and applicable law.

About this article

Cite this article

Noorallahzadeh, M., Mosleh, M., Misra, N.K. et al. A novel design of reversible quantum multiplier based on multiple-control toffoli synthesis. Quantum Inf Process 22, 167 (2023). https://doi.org/10.1007/s11128-023-03918-1

Received:

Accepted:

Published:

DOI: https://doi.org/10.1007/s11128-023-03918-1