Abstract

The study and development of chip multi-processors (CMPs) are of utmost importance for the creation of future technologies. Devising a theoretical analysis of the micro-architecture model for the power/performance on CMPs is still a challenge. This paper addresses this problem by (1) introducing an analytical model for measuring the power and performance of a processor quantitatively, (2) analyzing the effects of resource division on power consumption and performance when executing a given benchmark, and (3) predicting the optimum number of cores to run the benchmark on. Our proposed analytically derived results show that in order to achieve power/performance gains, the optimum number of cores must be between 8 and 16.

Similar content being viewed by others

References

Borkar S (1999) Design challenges of technology scaling. IEEE Micro 19(4):23–29. doi:10.1109/40.782564

Agerwala T, Chatterjee S (2005) Computer architecture: challenges and opportunities for the next decade. IEEE Micro 25(3):58–69. doi:10.1109/MM.2005.45

Chandrakasan AP, Sheng S, Brodersen RW (1995) Low power cmos digital design. IEEE J Solid State Circuits 27:473–484

Donald J, Martonosi M (2006) Techniques for multicore thermal management: Classification and new exploration. In: Proceedings of the 33rd annual international symposium on computer architecture, ISCA ’06, pp 78–88. doi:10.1109/ISCA.2006.39

Li Y, Brooks D, Hu Z, Skadron K, Bose P (2004) Understanding the energy efficiency of simultaneous multithreading, in: Proceedings of the 2004 international symposium on low power electronics and design, ISLPED ’04, pp 44–49. doi:10.1145/1013235.1013251

Sasanka R, Adve SV, Chen Y-K, Debes E (2004) The energy efficiency of cmp vs. smt for multimedia workloads. In: Proceedings of the 18th annual international conference on supercomputing, ICS ’04, pp 196–206. doi:10.1145/1006209.1006238

Peng L, Peir J-K, Prakash TK, Staelin C, Chen Y-K, Koppelman D (2008) Memory hierarchy performance measurement of commercial dual-core desktop processors. J Syst Archit 54(8):816–828. doi:10.1016/j.sysarc.2008.02.004

Burd T (2001) General processor information, http://bwrc.eecs.berkeley.edu/CIC/summary/local/summary.pdf, last Modified, January 2001

N. U. Microelectronics Industrial Centre (2002) A brief history of microprocessors, http://mic.cnn.ac.uk/miclearning/modules/micros/ch1/micro01hist.html

Brey B (2003) The Intel Microprocessors, 6th edn. Prentice Hall, Upper Saddle River

Schauer B (2008) Multicore processors—a necessity. Tech. rep, Proquest Discovery Guides

Li J, Martinez JF (2005) Power-performance implications of thread-level parallelism on chip multiprocessors. In: Proceedings of the IEEE international symposium on performance analysis of systems and software, 2005, ISPASS ’05, pp 124–134. doi:10.1109/ISPASS.2005.1430567

Najaf-abadi HH, Choudhary NK, Rotenberg E (2009) Core-selectability in chip multiprocessors. In: Proceedings of the 2009 18th international conference on parallel architectures and compilation techniques, PACT ’09, pp 113–122. doi:10.1109/PACT.2009.44

Kaxiras S, Narlikar G, Berenbaum AD, Hu Z (2001) Comparing power consumption of an smt and a cmp dsp for mobile phone workloads. In: Proceedings of the 2001 international conference on compilers, architecture, and synthesis for embedded systems, CASES ’01, pp 211–220. doi:10.1145/502217.502254

Kadayif I, Kandemir M, Sezer U (2002) An integer linear programming based approach for parallelizing applications in on-chip multiprocessors. In: Proceedings of the 39th annual design automation conference, DAC ’02, pp 703–706. doi:10.1145/513918.514096

Moshovos A, Memik G, Falsafi B, Choudhary A (2001) Jetty: Filtering snoops for reduced energy consumption in smp servers. In: International symposium on high-performance computer, architecture, pp 85–96

Saldanha C (2001) Power efficient cache coherence. In: In Workshop on Memory Performance Issues

Elnozahy EN, Kistler M, Rajamony R (2003) Energy-efficient server clusters. In: Proceedings of the 2nd international conference on power-aware computer systems, PACS’02, pp 179–197, http://dl.acm.org/citation.cfm?id=1766991.1767007

Elnozahy M, Kistler M, Rajamony R (2003) Energy conservation policies for web servers. In: Proceedings of the 4th conference on USENIX symposium on internet technologies and systems-USITS’03, vol 4, pp 8, http://dl.acm.org/citation.cfm?id=1251460.1251468

Grochowski E, Ronen R, Shen J, Wang H (2004) Best of both latency and throughput. In: Proceedings of the IEEE international conference on computer design, ICCD ’04, pp 236–243, http://dl.acm.org/citation.cfm?id=1032648.1033367

Huh J, Burger D, Keckler SW (2001) Exploring the design space of future cmps. In: Proceedings of the 2001 international conference on parallel architectures and compilation techniques, PACT ’01, pp 199–210, http://dl.acm.org/citation.cfm?id=645988.674164

Ekman M, Stenstrom P (2003) Performance and power impact of issue-width in chip-multiprocessor cores. In: International conference on parallel processing, pp 359–368

Su C-L, Despain AM (1995) Cache design trade-offs for power and performance optimization: a case study. In: Proceedings of the 1995 international symposium on low power design, ISLPED ’95, pp 63–68. doi:10.1145/224081.224093

Heo S, Asanovi K (2004) Power-optimal pipelining in deep submicron technology. In: International symposium on low power electronics and design, pp 218–223

Borah M, Irwin MJ, Owens RM (1995) Minimizing power consumption of static cmos circuits by transistor sizing and input reordering. In: Proceedings of the 8th International Conference on VLSI Design, VLSID ’95, p 294, http://dl.acm.org/citation.cfm?id=832282.834658

Mudge T (2001) Power: a first-class architectural design constraint. Computer 34(4):52–58. doi:10.1109/2.917539

Herbert S (2007) Analysis of dynamic voltage/frequency scaling in chip-multiprocessors. In: International symposium on low power electronics and design

Rao R, Srivastava A, Blaauw D, Sylvester D (2004) Statistical analysis of subthreshold leakage current for vlsi circuits. IEEE Trans Very Large Scale Integr Syst 12(2):131–139. doi:10.1109/TVLSI.2003.821549

Srinivasan V, Brooks D, Gschwind M, Bose P, Zyuban V, Strenski PN, Emma PG (2002) Optimizing pipelines for power and performance. In: Proceedings of the 35th annual ACM/IEEE international symposium on microarchitecture, MICRO 35, pp 333–344, http://dl.acm.org/citation.cfm?id=774861.774897

The itrs technology working groups, international technology roadmap for semiconductors (itrs), http://www.public.itrs.net

Meng K, Joseph R, Dick RP, Shang L (2008) Multi-optimization power management for chip multiprocessors. In: Proceedings of the 17th international conference on parallel architectures and compilation techniques, PACT ’08, pp 177–186. doi:10.1145/1454115.1454141

Ghasemazar M, Pakbaznia E, Pedram M (2010) Minimizing the power consumption of a chip multiprocessor under an average throughput constraint, in: ISQED’10, pp 362–371

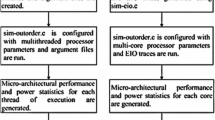

Burger D, Austin TM (1997) The simplescalar tool set, version 2.0, SIGARCH Comput Archit News 25(3):13–25. doi:10.1145/268806.268810

Author information

Authors and Affiliations

Corresponding author

Additional information

M.S. Obaidat is the fellow of IEEE and SCS.

Rights and permissions

About this article

Cite this article

Vijayalakshmi, S., Anpalagan, A., Kothari, D.P. et al. An analytical study of resource division and its impact on power and performance of multi-core processors. J Supercomput 68, 1265–1279 (2014). https://doi.org/10.1007/s11227-014-1086-0

Published:

Issue Date:

DOI: https://doi.org/10.1007/s11227-014-1086-0